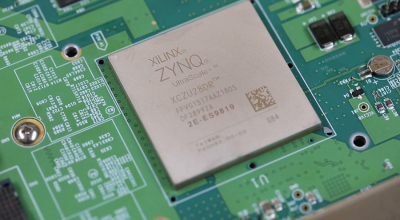

RFSoC应用笔记 - RF数据转换器(6):RFSoC关键配置之RF-ADC内部解析(四)

judy 在 周四, 12/22/2022 - 10:12 提交

本文主要对RFSoC ADC的可编程逻辑数据接口、多频带操作、以及奈奎斯特区的操作进行介绍。

本文主要对RFSoC ADC的可编程逻辑数据接口、多频带操作、以及奈奎斯特区的操作进行介绍。

本篇主要是闲谈个人对于Vitis AI的整个开发流程的理解,主要是想帮助一下新手快速找到一个开发目标

今天,机器人开发人员对 AMD Kria™ KR260 机器人入门套件的发布充满期待

通过本文可以学习以下内容:TX Buffer(缓冲器)的结构及使用,TX PRBS(伪随机序列)产生器的使用。

对于系统设计工程师来说,时序问题在设计中是至关重要的

该视频概述了如何设置和操作 Kria KR260 TSN ROS Pub/Sub 示例应用。

本文讲述了如何对上述情况进行分析,以便用户能更好的理解Scan Clear和MBIST的功能。

前一篇我们主要以单片机为例子讲述了FPGA和单片机内部结果的差异来解释“现场可编程的门阵列”

这次用KR260,我们挑战了一下更高难度,想尝试一下实际开发起来是一种怎样的体验

本文参考官方手册,主要对RFSoC ADC的校准机制进行介绍。