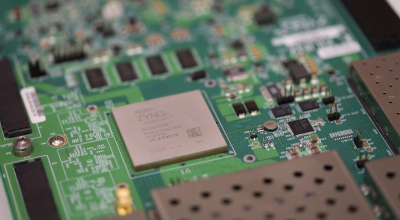

RFSoC应用笔记 - RF数据转换器(4):RFSoC关键配置之RF-ADC内部解析(二)

judy 在 周五, 12/16/2022 - 09:14 提交

本文参考官方手册,主要对RFSoC ADC的数字数据路径相关功能进行介绍。

本文参考官方手册,主要对RFSoC ADC的数字数据路径相关功能进行介绍。

对于工业企业而言,推进数字化转型至关重要,以此才能保持竞争力,并为客户提供价值

Xilinx越来越多的例程,给出的参考设计是基于Block Design设计方法的

本文我们继续介绍FPGA收发器TX结构和功能。

在日常的编码过程中,常常碰到一个参数会被到处调用的情况,比如时钟的定义和调用

本文我们就来具体看一下,为什么FPGA能够在数据中心加速领域领跑?具体的优势有哪些?

为什么要修改IP核内的源码,说如何之前,先说为什么。

本文主要对RFSoC的ADC内部结构以及数字步进衰减器和过压功能进行介绍。

本文介绍以下内容:GTX/GTH收发器TX结构,GTX/GTH收发器TX接口配置和时钟方案

Verilog的编译和C语言的编译二者自然不可同日而语,具体到FPGA的开发