Vitis开发(一):Vivado启动vitis

francis zhang 在 周三, 11/30/2022 - 10:32 提交

Vitis是Xilinx SDK的继承开发工具,从Vivado 2019.2版本开始启用

Vitis是Xilinx SDK的继承开发工具,从Vivado 2019.2版本开始启用

本博文主要对GTX/GTH收发器进行总体概述。

该款计算实例基于阿里云自研CIPU与磐久服务器,搭载AMD公司最新发布的第四代AMD EPYC(霄龙)处理器

Vitis 应用加速开发流程提供了相应的框架,可通过使用标准编程语言来为软件和硬件组件开发和交付 FPGA 加速应用

随者FPGA设计的日益复杂,设计实践、方法和流程逐渐成为重要的成功因素

宜鼎 FPGA平台采用科技巨擘 AMD XILINX KRIA K26 系统模块,不仅能够加速 AI 算法,同时具备低延迟

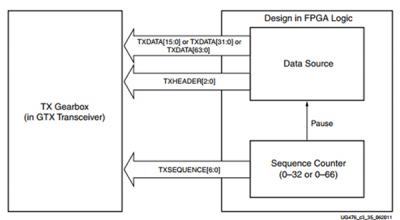

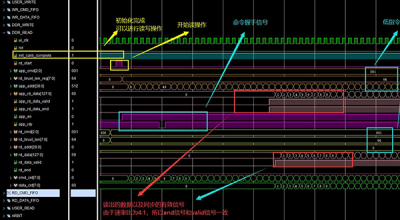

本文主要讲transceiver与用户逻辑数据的接口

Vitis-AI在边缘计算设备的AI全栈部署框架中扮演了编译器端与后端的角色,接收前端 DNN 框架训练后的网络参数IR

在之前设计的 DDR3 控制器的基础上,添加用户写、读模块,便于在用户端更容易的对 DDR3 进行写读控制

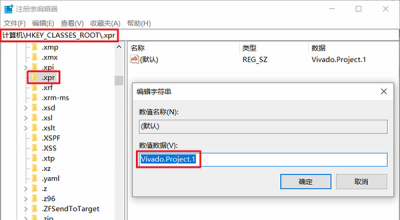

之前安装的Vivado 2018.3,最近装了Vivado 2020.2,然后就没法双击打开xpr工程文件了