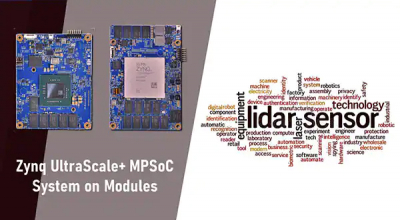

用于 LiDAR 的 Zynq UltraScale+ MPSoC 系统级模块

judy 在 周二, 11/15/2022 - 16:18 提交

Zynq UltraScale+ MPSoC 器件实现了基于 SoC 的自适应产品设计,这给 LiDAR 应用实现带来了非常大的前景

Zynq UltraScale+ MPSoC 器件实现了基于 SoC 的自适应产品设计,这给 LiDAR 应用实现带来了非常大的前景

Xilinx的FPGA开发板可以直接调用RAM,其中包括了BRAM和DRAM。

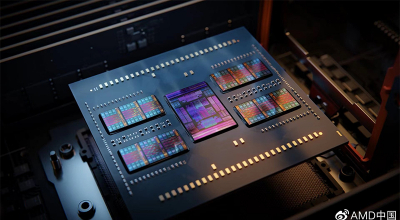

AMD 正在推出越来越多的 CPU 变体。虽然 CPU 用于通用工作负载,但针对各种终端市场的定制正在增加

在本文中,您将了解最常见问题的来源及其解决方案,以及如何将这些思想应用到您的设计中

本文缕缕时钟到底是哪来的,以及要起什么作用

双fifo流水线实现3x1024数组数据按列相加

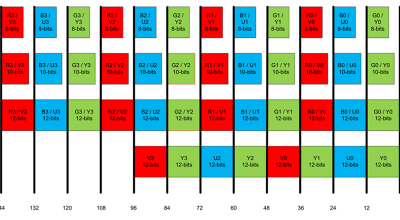

本文主要介绍使用AXI4S(AXI4-Stream)接口的视频IP细节。

在Petalinux配置工程时,会遇到如下类型文件系统。常用的有INITRAMFS、INITRD和EXT4

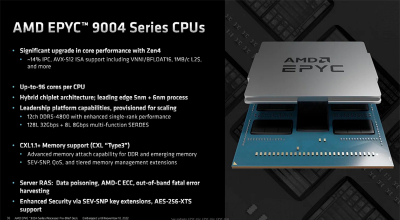

第四代AMD EPYC处理器,可提供卓越的性能、业界领先的能效和下一代架构。

在Windows下Vivado默认使用的是2线程,编译较慢。可改为32线程使Vivado可使用更多计算机资源,以加快编译速度