DFX流程(2)——非项目模式下的DFX

judy 在 周三, 11/23/2022 - 10:09 提交

Vivado同时支持在工程模式以及非工程模式中使用DFX流程,这里我们先从非工程模式开始介绍。

Vivado同时支持在工程模式以及非工程模式中使用DFX流程,这里我们先从非工程模式开始介绍。

在GTX/GTH收发器 TX链路中有两个内部并行时钟作用于PCS:PMA并行时钟(XCLK)和TXUSRCLK时钟域

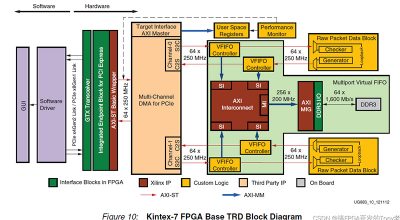

FPGA开发,虽然说行业应用千奇百怪,但是回归到平台设计这款,对外无非接口,对内无非片内总线

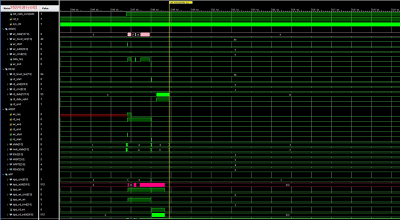

在实验的基础上添加一个仲裁模块,控制写读指令的执行。

从Ultrascale/Ultrascale+器件开始,大多数类型的逻辑资源都可以放到动态区域内,使得DFX功能的应用场景大大增加。

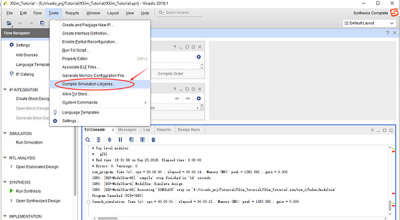

vivado软件切换使用modelsim仿真时,如果出现如下图所示情况

AMD高级副总裁、大中华区总裁潘晓明在演讲时表示,计算领域在未来将发生深刻的变革

在 2019.2 以上的版本中AMD-Xilinx去除了对 OpenCV 的库函数的直接支持,需要我们手动搭建一个OpenCV

本文主要介绍三个部分:DFX的基本流程、AS的环境搭建、AS的具体执行

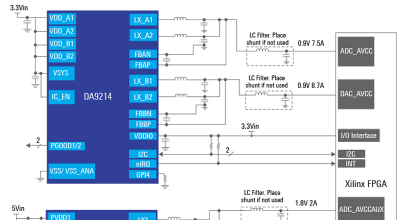

经过优化的、具有可编程开关频率的控制回路方案可提供快速瞬态响应,以减少外部组件的数量。