MIPI-DSI概述

judy 在 周五, 11/25/2022 - 09:55 提交

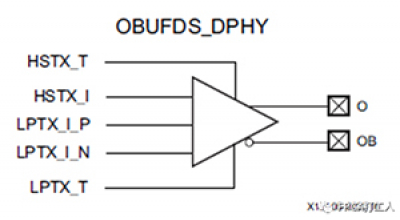

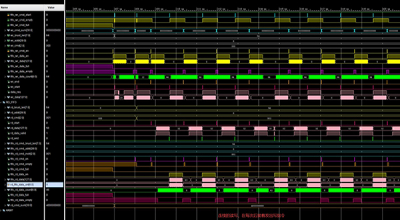

新的DSI-2协议定义了两个高速串行数据传输接口选项

新的DSI-2协议定义了两个高速串行数据传输接口选项

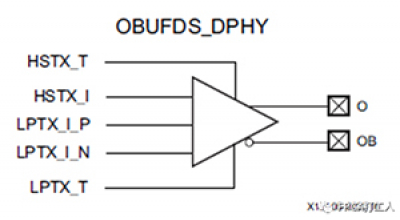

在读写模块的基础上添加 FIFO 接口,包括写指令 FIFO、写数据 FIFO

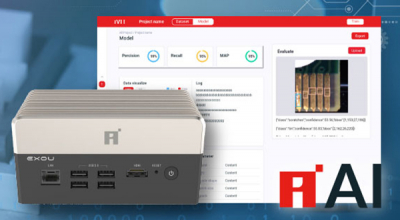

宜鼎FPGA平台采用AMD Xilinx Kria K26系统模块,不仅能够加速AI演算,同时具备低延迟、低功耗特性

跨时钟域设计(CDC)是个老生常谈的问题,各种笔面试都很喜欢考。其场景很多很杂

具有该性能水平的 SoC 片上系统需要大电流电源,并且要求电源具有可靠的稳压性能和抖动极低的时钟源。

最近遇到了一个vivado的报错,也算是一个比较低级的错误了,但是有值得思考的地方,这里分享下。

如果按照市值计算,Advanced Micro Devices今年是首次超越了英特尔,并创造了历史

Vivado同时支持在工程模式以及非工程模式中使用DFX流程,这里我们先从非工程模式开始介绍。

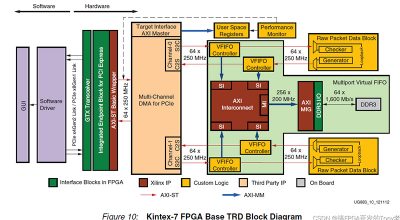

在GTX/GTH收发器 TX链路中有两个内部并行时钟作用于PCS:PMA并行时钟(XCLK)和TXUSRCLK时钟域

FPGA开发,虽然说行业应用千奇百怪,但是回归到平台设计这款,对外无非接口,对内无非片内总线