Vivado联合Modelsim软件安装和仿真库编译

francis zhang 在 周五, 10/28/2022 - 15:31 提交

Vivado hls工具与Vitis统一软件平台的出现和发展,突破了以往使用FPGA进行设计时,使用语言HDL语言进行设计实现的瓶颈

Vivado hls工具与Vitis统一软件平台的出现和发展,突破了以往使用FPGA进行设计时,使用语言HDL语言进行设计实现的瓶颈

在这个项目中,我们将创建一个简单的函数,将彩色图像转换为灰度图像

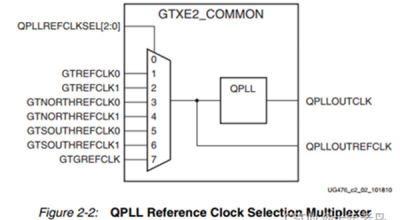

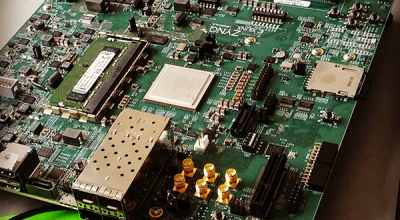

从IP核的时钟配置来学习transceiver的参考时钟架构细节

由于UG1029已经对LINUX下dfu-util的操作步骤做了详细说明,本文介绍WIN10下dfu-util的操作步骤

通过阅读IP手册可以知道,该IP支持的很多种浮点数计算,今天主要介绍最简单的加法操作

本工程实现PCIE的8通道速率2.2GBps通信,并验证数据的正确性

说到 FPGA ,不得不提的是存储器,当我们做相关项目时,经常会遇到存储数据的问题

视觉AI应用发展至今,已经遍地开花,你能想到的或想不到的地方,它都存在

随着机器人专家不断面临传统处理器架构带来的局限性,他们需要定制化和并行性来应对未来的性能、数据安全和运行安全挑战

本次开发者网络研讨会系列将分为三个章节,将分别演示如何集成深度学习处理单元