基于FPGA的数字信号处理(4)--如何确定Verilog表达式的位宽

judy 在 周五, 09/13/2024 - 09:23 提交

很多时候,Verilog中表达式的位宽都是被隐式确定的,即使你自己设计了位宽,它也是根据规则先确定位宽后,再扩展到你的设计位宽

很多时候,Verilog中表达式的位宽都是被隐式确定的,即使你自己设计了位宽,它也是根据规则先确定位宽后,再扩展到你的设计位宽

R2024b 推出了几项重要更新,帮助从事无线通信系统、控制系统和数字信号处理应用的工程师和研究人员简化工作流。

安路科技PH系列FPGA定位高性价比可编程逻辑市场,针对高带宽应用场景,能够在保持低功耗的前提下,提供同类更佳的收发器和信号处理功能

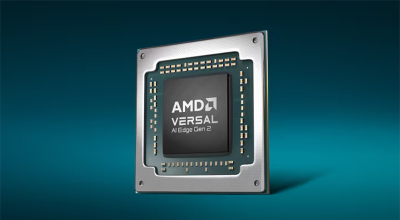

AMD首席执行官苏姿丰(Lisa Su)发表讲话称,人工智能的超级周期才刚刚开启,而AMD将瞄准英伟达的市场主导者地位,加速推出高性能人工智能芯片。

今天,我们一起来探讨三态门的基本原理、在Verilog中的实现方式。

我们在正常升级的过程(只使用一个位流文件),假如:(1)因为干扰通信模块收到了一个错误位;(2)或者烧写进FLASH时突然断电

工业领域的工厂长期以来一直使用数字数据来监视和控制生产设施。工厂、数据中心和商业建筑中的大型网络系统一直在将其数字信息网络的边缘越来越近地推向现实物理世界

随着大模型的快速发展,人工智能正在改变嵌入式硬件系统。AI处理重心向边缘转移,已经是行业共识。各类端侧AI应用,也已开始竞相布局。

我们很高兴地宣布 AMD Alveo 媒体加速产品组合( AMA )SDK 1.2 版本正式发布,进一步扩展 AMD Alveo MA35D 媒体加速卡功能。

第二代 Versal™ AI Edge 系列自适应 SoC 旨在通过增强的处理器系统、功耗优化的下一代 AI 引擎以及 AMD 全球领先的可编程逻辑来提升 AI 驱动型应用的系统级性能