最酷的 FPGA 技术之一:DFX 实例精讲

judy 在 周一, 09/09/2024 - 09:28 提交

本文将探讨神经形态计算的发展历程、关键器件及其测试参数,并讨论当前面临的挑战和解决方案。

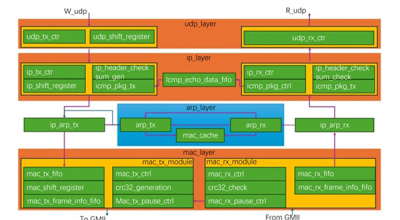

前面我们介绍了以太网的基本概念,及涉及的各层协议格式,接下来我们通过设计Verilog程序来实现以太网各个子层的功能

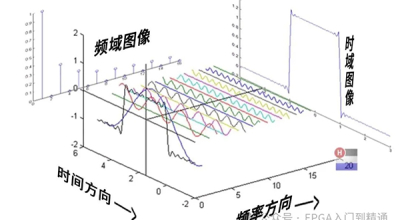

今天,就让我们一同深入这个充满魅力的数字信号处理基础——频域世界。

这款超紧凑的弹性存储芯片提高了SWaP,可用于通信、地球观测、科学和边缘计算卫星等高级任务。

Verilog中的signed是一个很多人用不好,或者说不太愿意用的一个语法。因为不熟悉它的机制,所以经常会导致运算结果莫名奇妙地出错

FIFO是FPGA项目中使用最多的IP核,一个项目使用几个,甚至是几十个FIFO都是很正常的。通常情况下,每个FIFO的参数,特别是位宽和深度,是不同的

随着人类移动用户超过 71 亿,再加上无线机器对机器 (M2M) 连接日益增加,无线行业正经历着空前的需求高涨。工程师在设计无线系统和网络时面临的主要挑战是其复杂性

在写这篇文章时,我想了很多标题,但总感觉没有哪个能把文章的意思全都总结清楚的,所以我又起了副标题:断臂求生的Intel。

如今,在中国市场,不论是消费级 CPU、GPU 还是服务器 CPU,AMD 都有着不错的口碑,AMD 市场份额逐年快速增长。