YunSDR小课堂-AIE编程指南(第49讲)

judy 在 周五, 05/23/2025 - 09:22 提交

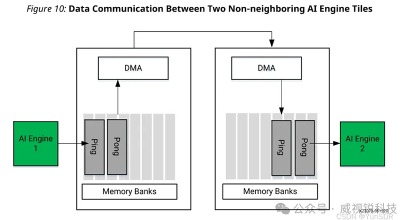

对于非相邻AI引擎,可以使用与每个AI引擎相关联的存储器模块中的DMA来建立类似的通信。在每个存储器模块中使用乒乓缓冲器,并通过锁进行同步

对于非相邻AI引擎,可以使用与每个AI引擎相关联的存储器模块中的DMA来建立类似的通信。在每个存储器模块中使用乒乓缓冲器,并通过锁进行同步

在AI Engine阵列配置中有两种顶级方案:通电时的AI Engine阵列配置和AI Engine阵列部分重新配置。

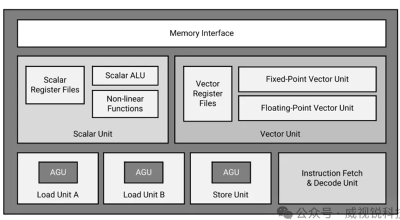

AI引擎中的算术逻辑单元(ALU)管理以下操作。在所有情况下,发行率都是每个周期一条指令。

AI Engine是一款高度优化的处理器,具有单指令多数据(SIMD)和超长指令字(VLIW)处理器,支持定点和浮点精度。

本节描述了AI Engine阵列内以及AI Engine Tile和可编程逻辑(PL)之间的数据通信示例。

AI Engine内存模块有32 KB的数据内存,分为八个存储体、一个内存接口、DMA和锁。传入和传出方向都有DMA,每个内存模块内都有一个Locks块

AMD Versal™自适应SoCs将标量引擎、自适应引擎和AI Engine与领先的内存和接口技术相结合,为任何应用提供强大的异构加速功能

通过重新检查先前考虑的Vivado工作流,可以突出强调协同设计方法。图11.10说明了Vivado和Vitis生态系统中的这种集成设计方法

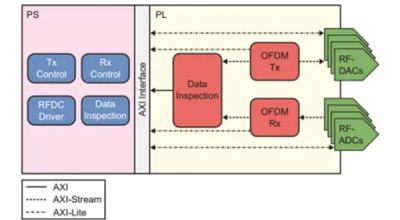

在设计RFSoC PS时,必须选择合适的软件堆栈来满足设计要求。软件栈是一组基本软件,开发人员可以在这些软件的基础上添加他们自己的定制软件

RFSoC器件分为两个主要的可定制部分,处理系统(PS)和可编程逻辑(PL)。在为RFSoC设计系统时,值得首先考虑的是设计的功能如何在这两个元素之间进行划分