YunSDR通信小课堂(第32讲)

judy 在 周四, 04/03/2025 - 16:25 提交

即使最好的数据转换器中也存在噪声和杂散,因此必须采用策略来减轻它们的影响,如频率规划。

即使最好的数据转换器中也存在噪声和杂散,因此必须采用策略来减轻它们的影响,如频率规划。

RF-DAC的数量、配置、结构和功能在不同的RFSoC设备和年代之间有所不同。图9.10突出显示了选定设备的RF-DAC在配置上的差异。

DAC的作用是将离散时间的数字采样转换为连续时间的模拟信号,通常使用零阶保持(ZOH)技术。该技术可被视为ADC中采样技术的对应项

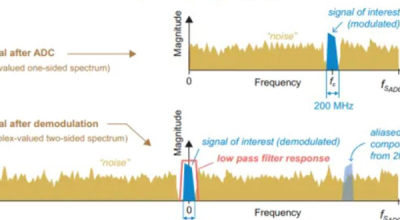

在本例中,使用4Gsps的RF-ADC采样率,模拟RF信号占据奈奎斯特一区的频谱,因此RF- ADC可以直接将其数字化如图10.2(a)所示。

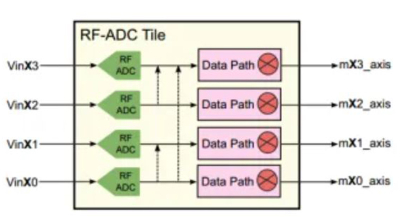

通过包含RF Data Converter IP核,可以将优化的RF- adc添加到任何RFSoC Vivado IP Integrator项目中

正如前面7.2节所讨论的,在RF-ADC之前,需要适当的放大和模拟滤波。如果接收到的射频信号通过滤波器、放大器等直接从天线到达

如前所述,RF- ADC能够接收射频频率高达几GHz的信号。一旦数字化,信号被解调,这样它就以0赫兹为中心。该操作的关键是每个RF-ADC中的数字复混频器

在某些情况下,可以利用混叠将信号折叠到奈奎斯特一区。折叠后可以用RF-ADC直接对第二奈奎斯特区的信号进行采样

大多数SDR架构需要数字上转换和下转换阶段,这些转换位于A/D和数字基带级之间,包括信号的频率转换和采样率的变化。

RFSoC平台作为最先进的现代SDR平台,可以使用FPGA可编程逻辑内核生成GHz带宽信号,上变频、滤波、数字预失真甚至射频载波调制都可以通过数字方式进行