基于FPGA的数字信号处理(3)--如何确定Verilog表达式的符号

judy 在 周二, 09/10/2024 - 14:58 提交

尽管signed语法的使用能带来很多便利,但同时也给表达式的符号确定带来了更多的不确定性。比如一个有符号数和一个无符号数的加法/乘法结果是有符号数还是无符号数?

尽管signed语法的使用能带来很多便利,但同时也给表达式的符号确定带来了更多的不确定性。比如一个有符号数和一个无符号数的加法/乘法结果是有符号数还是无符号数?

今天介绍一下并行 FIR 数字滤波器的原理以及实现。

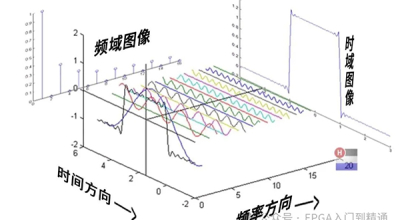

今天,就让我们一同深入这个充满魅力的数字信号处理基础——频域世界。

Verilog中的signed是一个很多人用不好,或者说不太愿意用的一个语法。因为不熟悉它的机制,所以经常会导致运算结果莫名奇妙地出错

数字电路中,小数可以用两种形式来表示:「定点数」和「浮点数」。浮点数的内容我们下篇文章再讲,本文只讲定点数。

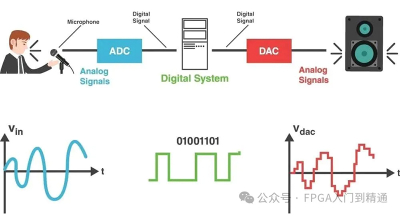

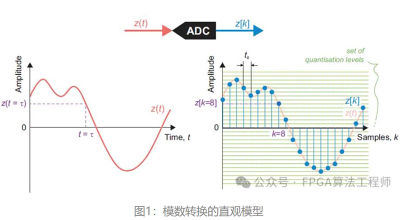

今天,我们将一起探索数字信号处理基础中至关重要的两个概念:连续信号离散化与采样定理。

本文将以通俗易懂的方式,让大家深入了解数字信号处理基础中的时域概念。

在数字信号处理的奇妙世界里!“信号”是一切的基础,理解了信号,就相当于拿到了开启数字信号处理大门的钥匙。

本文系摘录自《RFSoC SDR Book》第四章——DSP Fundamentals,略有改动。下面将介绍采样(Sampling)的基本概念

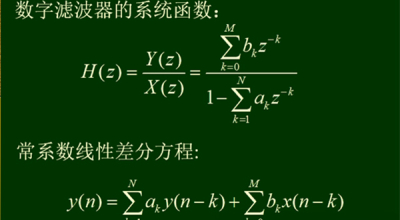

IIR滤波器具有很高的滤波效率,在相同幅频响应条件下,所需的滤波器阶数明显比FIR滤波器低