如何在Vivado中对RTL源文件进行加密

judy 在 周三, 02/08/2023 - 11:16 提交

本文介绍在使用源文件加密时的一些基本概念以及一些常见的问题

本文介绍在使用源文件加密时的一些基本概念以及一些常见的问题

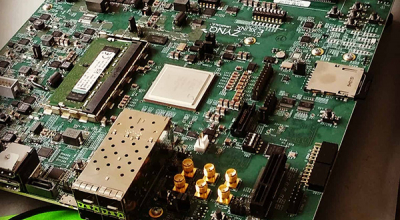

使用AMD、RFDSP、VIAVI和Rohde & Schwarz的设备演示基于Zynq RFSoC DFE的O-RAN前传和射频合规性

借助 Kria SOM,ProMik 能够对其在系统编程解决方案提速,从而实现高性能并行处理和闪存。

AMD EPYC处理器不仅带来出色的性能,而且能够进一步降低能耗

本文将侧重于概述如何以 ZCU106 开发板为目标,创建和运行仅限 TX 的设计

本文将介绍两种实现相位对齐的方法,可适用于US系列和US Plus系列的GTH和GTY器件

全新计划旨在提供基于 Kria SOM 的量产级、全功能解决方案,助力客户加速产品上市进程

本文简单介绍几种常见的图像格式以及Xilinx FPGA实现方式。

UltraScale器件中时钟管理模块(CMT)包含mixed-mode clock manager (MMCM) 和phase-locked loops (PLLs)

本文分析了FPGA可能暴露的主要漏洞,并介绍了可编程器件制造商所采用的作为防篡改措施的技术。