Versal Premium 系列:PCIe Gen5

judy 在 周四, 07/29/2021 - 09:42 提交

Versal™Premium 系列符合 PCIe® 规范修订版 5.0,并且通过每条通道每秒 32 千兆次传输的速度支持全部链路速率。该视频演示了 Versal Premium ACAP 中面向 PCIe 的两个可用子系统,这在下一代网络和云基础架构中至关重要。

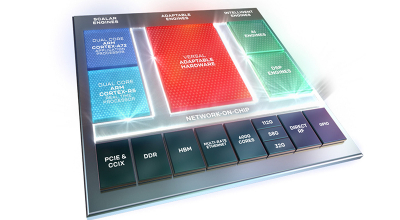

ACAP(Adaptive Compute Acceleration Platform)是赛灵思(Xilinx)公司提出的概念,表示一种自适应计算加速平台。ACAP 是在 FPGA(可编程门阵列)的基础上演进而来的,结合了 FPGA 的灵活性和可编程性以及 ASIC(专用集成电路)的性能和效率。

ACAP 旨在应对多样化、动态性和高度定制化的计算需求。与传统的 FPGA 不同,ACAP 具有更高级别的自适应性,能够在运行时重新配置其硬件架构,以适应不同的工作负载。这种动态适应性使得 ACAP 在处理各种任务时能够更加高效地利用硬件资源。

Versal™Premium 系列符合 PCIe® 规范修订版 5.0,并且通过每条通道每秒 32 千兆次传输的速度支持全部链路速率。该视频演示了 Versal Premium ACAP 中面向 PCIe 的两个可用子系统,这在下一代网络和云基础架构中至关重要。

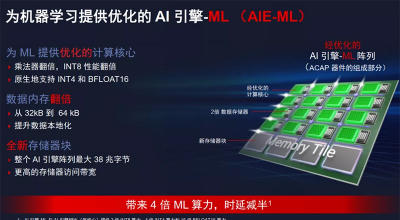

Xilinx 推出 Versal™ HBM 系列,在单个平台上融合了高速存储器、安全连接和自适应计算,面向计算最密集、内存受限、高带宽应用。

赛灵思今日宣布推出 Versal™ HBM 自适应计算加速平台( ACAP ),这是 Versal™ 产品组合的最新产品系列。Versal HBM ACAP 在单个平台上融合了高速存储器、安全连接和灵活应变的计算。该系列集成了最先进的 HBM2e DRAM,可提供 820GB/s 吞吐量和 32GB 容量,与 DDR5 1相比存储器带宽提高 8 倍、功耗降低 63%。

VERSALDEMO1Z 是一个和 Xilinx 联合开发的电源参考板,它为 Xilinx Versal ACAP 平台提供完整的电源轨,ACAP 平台包括自适应引擎、人工智能引擎和标量引擎,以及外部的 DDR 存储器。这款参考板已经开放订购,它既可以作为成熟的整套参考设计,帮助客户抢占设计先机,也可以作为评估平台,快速方便地进行电源测试。

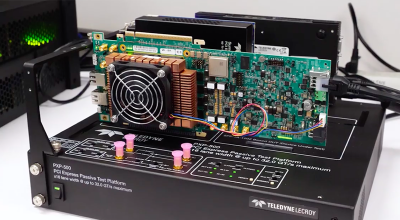

Versal Premium ACAP 系列符合 PCIe 规范修订版 5.0,并且通过每通道 32 GT/s 的传输速度支持全部链路速率。 本视频演示了 Versal Premium ACAP 中面向 PCIe 的两个可用子系统,这在下一代网络和云基础架构中至关重要。

如果 Arm Cortex-A72 处理器配置为向处于 UniqueClean (UC) 状态的缓存行发送逐出传输事务,那么 Cortex-A72 处理器可能返回陈旧数据并发出嗅探响应。

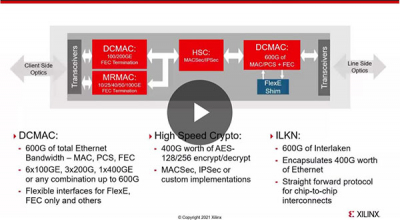

Versal Premium DCMAC 是一个集成块,可通过 100GE、200GE 或 400GE 的任何组合实现高达 600G 的以太网吞吐量。在本视频中,我们将简要介绍该模块的特性,并重点展示一些早期实验室测试结果。

在 aarch32 模式下,如果执行的代码包含下面的加密指令序列,并且在执行第一条加密指令后立即断言并中断,ELR 会被记录为返回地址,产生的错误可能会导致数据损坏

近几年,边缘计算市场在快速增长,速度超过了数据中心。有统计显示,到2025年,边缘AI芯片的市场机遇是数据中心的3倍,规模将达到650亿美元。这样具有巨大发展潜力的市场,是所有能够参与到其中的芯片厂商特别关注的,无论是CPU、GPU,还是FPGA。作为FPGA行业龙头,赛灵思也已经准备好推出相应的器件

就在三年多前,Victor Peng 在 Moshe Gavrielov 退休后接任 Xilinx 首席执行官一职。管理层的转变标志着公司新时代的开始,Peng开始将世界上最大的可编程逻辑公司转变为具有更广泛市场覆盖和增长潜力的公司。 那么,现在,三年后,Peng的 2018 年承诺如何站稳脚跟,Xilinx 下一步将走向何方?