用于密集型在轨边缘计算的微处理器和FPGA

judy 在 周五, 03/04/2022 - 17:57 提交

在这篇文章中,我想探讨和比较用于边缘密集型星载处理的微处理器和FPGA。一些应用需要从不同带宽的多个传感器获取大量数据,同时需要实时做出关键决策

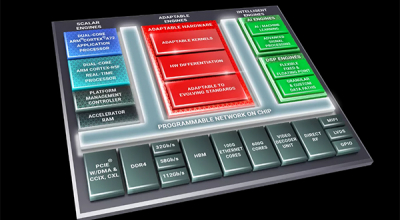

ACAP(Adaptive Compute Acceleration Platform)是赛灵思(Xilinx)公司提出的概念,表示一种自适应计算加速平台。ACAP 是在 FPGA(可编程门阵列)的基础上演进而来的,结合了 FPGA 的灵活性和可编程性以及 ASIC(专用集成电路)的性能和效率。

ACAP 旨在应对多样化、动态性和高度定制化的计算需求。与传统的 FPGA 不同,ACAP 具有更高级别的自适应性,能够在运行时重新配置其硬件架构,以适应不同的工作负载。这种动态适应性使得 ACAP 在处理各种任务时能够更加高效地利用硬件资源。

在这篇文章中,我想探讨和比较用于边缘密集型星载处理的微处理器和FPGA。一些应用需要从不同带宽的多个传感器获取大量数据,同时需要实时做出关键决策

该视频介绍了 Aupera 和 Xilinx 在 VCK5000 卡上采用的这种实现方法,以实现完整的视频处理和 ML 推断管道,以及低延迟和高吞吐量的 AI 识别结果。

过去几年里,计算行业见证了数据的大规模爆发以及机器学习( ML )与 AI 应用的激增。其结果是对更高吞吐量和实时计算能力愈发强烈的需求,与此同时还要保持灵活应变能力,以便跟上不断演进的工作负载需求和不断变化的协议。

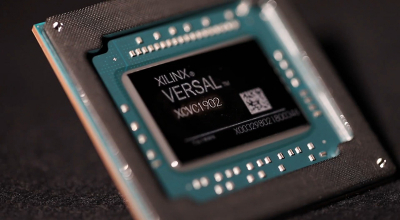

赛灵思 Versal® 自适应计算加速平台 (ACAP) 设计方法论是旨在帮助精简 Versal 器件设计进程的一整套最佳实践。

本文描述 AI引擎的编程环境。

2021 年 4 月,赛灵思取得了令人激动的阶段性成果——宣布业界领先的 Versal™ AI Core 和 Versal Prime 系列器件实现全面量产和付运。如同我们的宇宙一样,Versal 生态系统也在持续迅速扩张,涵盖更加广泛

本文描述了Vivado®设计套件中使用的电路设计元素,并与带有AI内核的Versal™ ACAP器件相关。元素细节包括VHDL和Verilog实例化代码、原理图符号、真值表以及设计元素的其他特定信息。

对于任何一项设计,要想尽可能实现最低的功率包络,都需要在设计周期早期准确估算功耗。早期估算有助于选择合适的器件、充分发挥架构优势、更改设计拓扑,以及使用不同 IP 块。在设计阶段早期妥善权衡取舍,可以帮助用户在满足规格要求的同时,将自身产品更快速推向市场。本文档旨在介绍如何根据 Versal™ ACAP 架构的描述来使用 Xilinx Power Estimator (XPE)。

赛灵思 Versal™ 自适应计算加速平台 (ACAP) 设计方法论是旨在帮助精简 Versal 器件设计进程的一整套最佳实践。鉴于这些设计的规模与复杂性,因此必须通过执行特定步骤与设计任务才能确保设计每个阶段都能成功完成。本指南将分为以下五大章节,遵循指南里的步骤和最佳实践进行操作,将有助于您以尽可能最快且最高效的方式实现期望设计目标。

赛灵思今日宣布,双方正合作开发 NEC 的下一代 5G 无线电单元( RU),预计 2022 年可用于全球部署。赛灵思 7nm Versal AI Core 系列器件现已量产出货,将助力全新 NEC RU 实现更出色的性能。这些最新型 NEC 5G 大规模 MIMO RU 利用数字波束成形带来更高效的通信和更高带宽。NEC RU 旨在满足全球市场需求,将支持C-Band 在内的多种 5G 频段。