AI 加速助力医学成像技术

judy 在 周三, 02/22/2023 - 10:20 提交

3月23日,由AMD举办的在线研讨会上,我们将详细为您介绍这款最新发布的医疗成像库

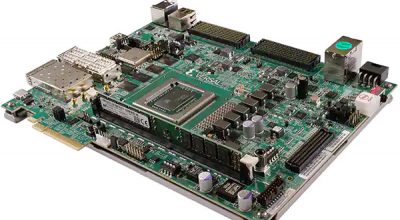

ACAP(Adaptive Compute Acceleration Platform)是赛灵思(Xilinx)公司提出的概念,表示一种自适应计算加速平台。ACAP 是在 FPGA(可编程门阵列)的基础上演进而来的,结合了 FPGA 的灵活性和可编程性以及 ASIC(专用集成电路)的性能和效率。

ACAP 旨在应对多样化、动态性和高度定制化的计算需求。与传统的 FPGA 不同,ACAP 具有更高级别的自适应性,能够在运行时重新配置其硬件架构,以适应不同的工作负载。这种动态适应性使得 ACAP 在处理各种任务时能够更加高效地利用硬件资源。

3月23日,由AMD举办的在线研讨会上,我们将详细为您介绍这款最新发布的医疗成像库

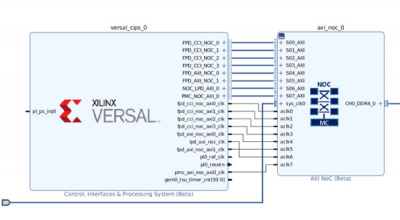

Versal 系列的DMA axi bridge模式可以在PL的QDMA IP或者在CPM的QDMA IP中选中

传统的射频收发器采用的是外差式结构。发射或接收的模拟射频信号通过带有本地振荡器的混频器

本文介绍了如何开启Versal最基本的XilSEM功能。

Xilinx 的 Versal AI Core 系列器件旨在解决有关 AI 推理的最大而独特的难题

Versal™ 是由多个高度耦合的可配置块组成的自适应计算加速平台 (ACAP)

本文我们就来具体看一下,为什么FPGA能够在数据中心加速领域领跑?具体的优势有哪些?

新的8 GB版本在同样小巧和管脚兼容的外形尺寸之下将存储密度提高了一倍

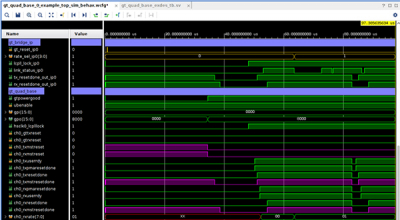

本篇博文侧重于提供 Versal™ GTY 仿真示例、演示 GTY 如何解复位以及如何执行速率变更。

了解 Versal 器件功耗估计从 XPE 迁移到 PDM 的简易迁移路径,并展示了其易用性和增强型向导。