Versal ACAP DDRMC - DDR4、LPDDR4 和 LPDDR4X 外部参考时钟设计指南文章

judy 在 周五, 04/21/2023 - 16:55 提交

本文旨在呈现使用 DDR4、LPDDR4 或 LPDDR4X 存储器控制器的 Versal ACAP 器件的外部参考时钟电路要求

ACAP(Adaptive Compute Acceleration Platform)是赛灵思(Xilinx)公司提出的概念,表示一种自适应计算加速平台。ACAP 是在 FPGA(可编程门阵列)的基础上演进而来的,结合了 FPGA 的灵活性和可编程性以及 ASIC(专用集成电路)的性能和效率。

ACAP 旨在应对多样化、动态性和高度定制化的计算需求。与传统的 FPGA 不同,ACAP 具有更高级别的自适应性,能够在运行时重新配置其硬件架构,以适应不同的工作负载。这种动态适应性使得 ACAP 在处理各种任务时能够更加高效地利用硬件资源。

本文旨在呈现使用 DDR4、LPDDR4 或 LPDDR4X 存储器控制器的 Versal ACAP 器件的外部参考时钟电路要求

本文旨在呈现 Versal HBM 器件的外部参考时钟电路要求

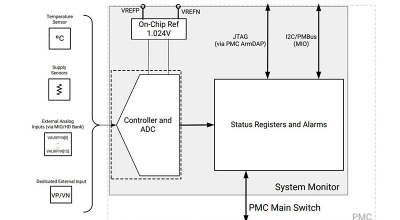

全新平台管理控制器 (PMC) 中的 Versal SYSMON 在启动时提供快速寄存器访问

如果 route_design 多次运行且在硬件中不切换路径

抱着手机刷短视频、看各种直播已经成为人们休闲娱乐的主要方式。

AMD 赛灵思 Video SDK 3.0 为功能已十分丰富的 Video SDK 2.0 带来了进一步强化

本文概述了基于ASIC的新型加速器旨在解决的问题,介绍了该设备的主要功能

支持 AI 的智能视频管道以较低的比特率实现最佳视频质量,从而降低带宽成本

Alevo MA350D增加了对AV1的支持,可以同步处理32条1080p视频流,压缩率提升80%

AMD Xilinx 视频 SDK 已发布,对于每一毫秒都很重要的实时流媒体应用,现在可通过内部安装向 Alveo U30 媒体加速器用户提供