Versal家族到底都有哪些兄弟姐妹

judy 在 周五, 05/20/2022 - 13:41 提交

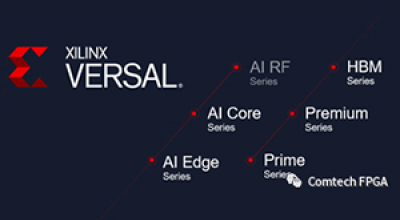

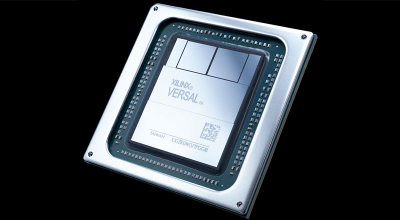

面向不同应用,Versal家族有AI Core, AI Edge , AI RF,Prime, Premium,HBM,六个系列、名字看起来是不是十分复杂?今天让我们来和您好好唠唠Versal系列这兄弟姐妹六系列!

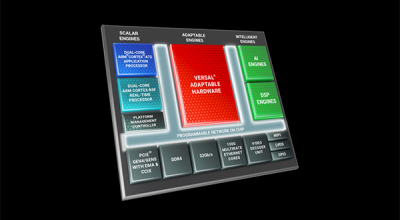

ACAP(Adaptive Compute Acceleration Platform)是赛灵思(Xilinx)公司提出的概念,表示一种自适应计算加速平台。ACAP 是在 FPGA(可编程门阵列)的基础上演进而来的,结合了 FPGA 的灵活性和可编程性以及 ASIC(专用集成电路)的性能和效率。

ACAP 旨在应对多样化、动态性和高度定制化的计算需求。与传统的 FPGA 不同,ACAP 具有更高级别的自适应性,能够在运行时重新配置其硬件架构,以适应不同的工作负载。这种动态适应性使得 ACAP 在处理各种任务时能够更加高效地利用硬件资源。

面向不同应用,Versal家族有AI Core, AI Edge , AI RF,Prime, Premium,HBM,六个系列、名字看起来是不是十分复杂?今天让我们来和您好好唠唠Versal系列这兄弟姐妹六系列!

AMD收购赛灵思的目的在于将其差异化IP集成到公司未来旗下的CPU中,Xilinx无论是从丰富的计算引擎还是其AI引擎技术都能让AMD在服务器CPU市场上扩大影响力

本文描述在 Versal® ACAP 中实现电源排序的各种方法。

Vivado® ML 2022.1 在 Vivado ML 标准安装中可支持 Versal Premium VP1202、VP1502、VP1702 和 VP1802 器件。

以下是在 Vitis™ 软件平台中创建 Platform Loader and Manager (PLM) elf 文件的步骤。在 Versal™ 器件中,PLM 在 PMC 内执行,并用于引导 APU 和 RPU。

本章用于演示如何为 Versal™ ACAP 集成和加载引导加载程序、裸机应用(针对 APU/RPU)和 Linux 操作系统。

我们早已迫不及待,此刻终于可以正式发布搭载 AI 引擎的 Versal Premium 系列。新一代无线系统要求高性能信号处理,并能够处理进出计算器件的海量数据。

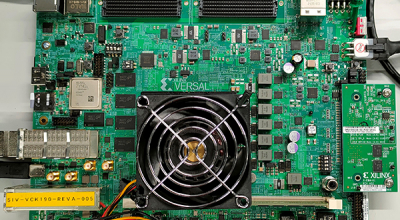

本教程对应目标为 Versal ACAP VCK190 和 VMK 180 评估板。本教程中的示例已使用 VCK190 ES1 评估板经过测试。要使用本教程,您需要具备以下硬件项,这些硬件项均随附于该评估板中

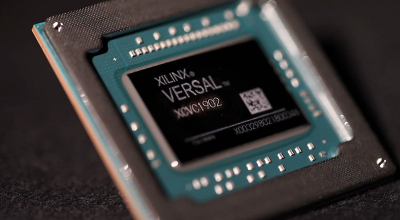

从数据中心到边缘部署,我们的 7nm Versal® 自适应计算加速平台( ACAP ) 产品组合持续在多个行业迎来重要里程碑。今天,我们很高兴宣布,Versal HBM 系列现正面向早期试用客户出货。

本文说明了在Xilinx® Versal® AI Core器件上实现任意重采样的情况,其中控制器在可编程逻辑中,而繁重的计算被映射到AI引擎中。