Xilinx RFSOC GEN1 ADC和DAC简单测试

wyh102 在 周二, 01/03/2023 - 10:43 提交

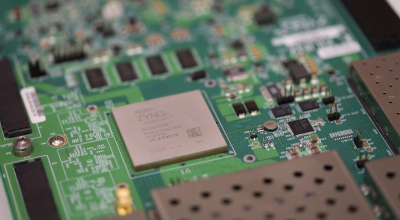

RFSOC-27DR产品是基于Zynq UltraScale + RFSoC ZU27DR主芯片的VPX平台评估板

RFSOC-27DR产品是基于Zynq UltraScale + RFSoC ZU27DR主芯片的VPX平台评估板

本文主要对RFSoC的ADC内部结构以及数字步进衰减器和过压功能进行介绍。

应用笔记简要描述Xilinx Zynq 系列器件XADC的相关资源及若干种应用

RS码是一种常用的纠错编码,本文主要介绍如何在vivado环境下利用RS IP核实现RS码的编译码。

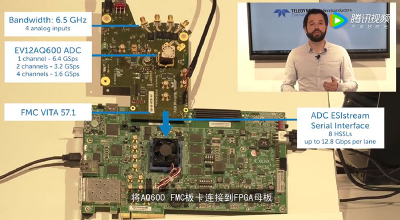

本视频教程阐述了如何创建一个Vivado工程,以及如何基于VHDL设计案例和EV12AQ600-ADX-EVM演示板,在Kintex Ultrascale FPGA上实现ADX4 IP。

DX4 - 与Xilinx Kintex® Ultrascale FPGA兼容的后处理算法可在宽带应用中提供高达10 dBFS的SFDR动态杂散抑制和接近1个有效位的额外分辨率。

本视频带您学习如何简单地下载并创建Vivado工程,实现ADC EV12AQ600/605的串行接口,并缩短您的开发时间。

为满足低电压数字讯号(LVDS)和并行输出ADC的需要,延迟不一致的问题,对系统设计人员而言是一个难题

本文介绍了使用16通道发射(16Tx)和16通道接收(16Rx)子数组的实验结果,其中所有发射和接收信道都使用数字转换器集成电路(IC)中的强化型DSP模块来校准。与其它架构相比,这个多信道系统在尺寸、重量和功率上都更有优势。相对于该系统的FPGA资源利用率后可发现,强化型DSP模块可为多信道平台的设计人员解决重要挑战。

在本视频中,我们展示了在 XCZU47DR 器件的双模块中使用两个 5GSPS ADC 的 10GSPS ADC 性能。