FPGA图像处理(6)常用算法:RGB图像转灰度图像

demi 在 周二, 12/10/2019 - 16:01 提交

RGB 图像转灰度图像的计算,即由当前像素点的 RGB 值计算 YUV 色域的 Y 通道的数值

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

RGB 图像转灰度图像的计算,即由当前像素点的 RGB 值计算 YUV 色域的 Y 通道的数值

在进行加减乘除运算时一定要注意位宽,保证足够大的位宽,防止数据溢出,如果溢出结果就会出现错误,尤其是加和乘运算,一定要计算好位宽(位宽的计算可以都取其最大值,看最大值计算后的位宽就是最大位宽,采用这个位宽数据就溢出不了)。

回想一下平时我们常用的复位方式:1.首先,上电后肯定是要复位一下,不然仿真时会出现没有初值的情况;2.最好有个复位的按键,在调试时按一下复位键就可以全局复位了;3.也许是同步复位,也许是异步复位,不同的工程师可能有不同的方案。

在10月份举办的 2019 XDF 上,赛灵思CEO Victor Peng 邀请亚马逊网络服务 (AWS) 业务发展高级总监 Gadi Hutt、亚马逊 Sagemaker Neo 及 AWS 人工智能工程总监 Vin Sharma 登台,通过分享双方基于FPGA 即服务 (FaaS) 紧密技术合作所创造的一系列成果,展示了领先企业技术合作的宝贵价值。

对于设计者来说,当然希望我们设计的电路的工作频率尽量高。我们也经常听说用资源换速度,用流水的方式可以提高工作频率,这确实是一个很重要的方法,今天我想进一步去分析该如何提高电路的工作频率。

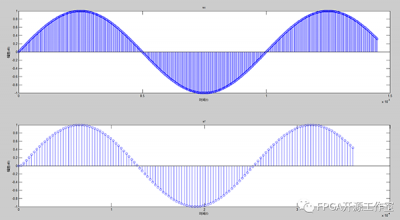

在《基于FPGA的多级CIC滤波器实现四倍抽取一》和《基于FPGA的多级CIC滤波器实现四倍抽取二》中我们先来了解滑动平均滤波器、微分器、积分器以及梳状滤波器原理以及它们的幅频响应。此篇我们将用verilog实现基于FPGA的多级CIC滤波器实现四倍插值。

图像直方图用来反映一副图像的像素分布。其中,横坐标表示图像像素的灰度级,纵坐标表示每个灰度级对应的像素总数或占所有像素个数的百分比。

在《基于FPGA的多级CIC滤波器实现四倍抽取一》和《基于FPGA的多级CIC滤波器实现四倍抽取二》中我们先来了解滑动平均滤波器、微分器、积分器以及梳状滤波器原理以及它们的幅频响应。在三中我们将用verilog实现基于FPGA的多级CIC滤波器实现四倍抽取。

忠告一:如果时序差的不多,在1NS以内,可以通过修改综合,布局布线选项来搞定,如果差的多,就得动代码。

在实现多级CIC滤波器前我们先来了解滑动平均滤波器、微分器、积分器以及梳状滤波器原理。CIC滤波器在通信信号处理中有着重要的应用。