有关 UltraScale HW-SYSMON 的设计咨询:I2C 接口上意外启用写操作的安全性隐患

judy 在 周二, 12/08/2020 - 10:22 提交

在 I2C 接口中意外启用写入时, UltraScale 器件的 HW-SYSMON 出现问题。这将使攻击者可直接写入接口。

在 I2C 接口中意外启用写入时, UltraScale 器件的 HW-SYSMON 出现问题。这将使攻击者可直接写入接口。

本用户指南介绍了UltraScale架构的PCB设计和引脚规划资源。

本指南提供有关使用、定制和仿真 DDR3 或 DDR4 SDRAM、LPDDR3 SDRAM、QDR II+ SRAM、QDR-IV SRAM 或 RLDRAM 3 接口内核的信息。它还描述了内核架构,并提供了定制和与内核接口的细节。

本视频围绕 UltraScale 和 UltraScale+ 架构,回顾了 DFX 布局规划基本信息;并提供了通过创建更优化的布局规划来改善设计结果的策略和技巧。

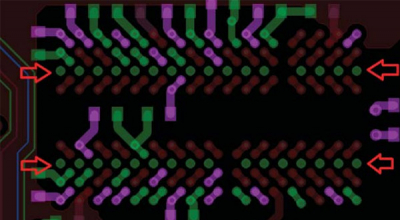

最近用了赛灵思最新UltraScale系列芯片,然后就拿着赛灵思的UG好好研究了一番。发现这个这个系列的FPGA跟ZYNQ相比有了改变,原来ZYNQ是一个CLB包含2个SLICE,然后每个SLICE同时又包含4个6输入LUTS。

FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者原语的方式来进行乘法操作。在里面可以设置有符号还是无符号数乘法。

Xilinx® UltraScale™架构是第一个ASIC级架构,可通过智能处理实现每秒数百吉比特的系统性能,同时有效地路由和处理片上数据。

本文档提供了为Xilinx®Zynq®UltraScale +™MPSoC器件设计和开发系统软件和应用程序所需的以软件为中心的信息。

描述使用UltraScale™和UltraScale +™器件进行PCB和接口级设计的策略。

UltraScale™FPGA收发器向导用于配置和简化Xilinx®UltraScale或UltraScale +™器件中一个或多个串行收发器的使用。