OSERDESE3与ODELAYE3原语

judy 在 周日, 01/29/2023 - 09:51 提交

UltraScale 架构的器件 包括三种I/O:高性能(HP), 高密度 (HD),和高量程(HR) I/O banks

UltraScale 架构的器件 包括三种I/O:高性能(HP), 高密度 (HD),和高量程(HR) I/O banks

UltraScale器件中时钟管理模块(CMT)包含mixed-mode clock manager (MMCM) 和phase-locked loops (PLLs)

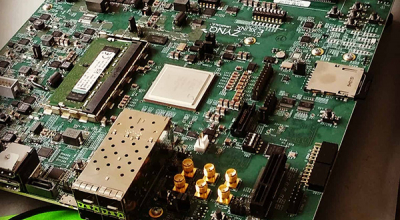

本文介绍Xilinx® UltraScale FPGA实现LVDS 1:7接收数据解串

让我们以一个简单的例子,FIR 滤波器,来看看如何写出能适配不同型号 FPGA 的代码。

LVDS是一种低摆幅的差分信号技术,使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

根据用户指南,要符合预配置 BSDL 文件描述要求,PUDC_B 应该设置为 1。在实际 BSDL 文件中,我只看到了 PROGRAM_B 的合规性:

UltraScale SEM IP 在从 Vivado IP 目录生成和从 IP 集成器目录生成时有一定的差异。这些差异是什么呢?UltraScale SEM 打算如何在 IP 集成器中使用?

在Serdes流行之前,芯片之间的数据传输主要靠低俗串行接口和并行接口,存在诸如传输速率低、占用IO数量多、硬件连接复杂化等弊端。Serdes的出现简化了数据传输接口的硬件设计,大大提升了数据传输的速率和带宽效率。 今天我们来聊一聊7 Series、Ultrascale系列GTH与Ultrascale+ GTY的内部区别。

本应用笔记提供了防篡改(AT)指南和实际案例,以帮助保护UltraScale™和UltraScale+™ FPGA启用的系统中可能存在的IP和敏感数据。

基于UltraScale架构的FPGA的封装和引脚规格不同。包括7系列FPGA在内的前几代产品。这些细节在此概述。