【下载】白皮书:利用偏移温度扩展散热解决方案

demi 在 周五, 10/25/2019 - 10:17 提交

一些UltraScale+™和Versal™设备提供了一个漂移温度,可以在有限的时间内将操作上限温度提高10°C。如果使用得当,这个特性可以扩展热解决方案的许多应用。

一些UltraScale+™和Versal™设备提供了一个漂移温度,可以在有限的时间内将操作上限温度提高10°C。如果使用得当,这个特性可以扩展热解决方案的许多应用。

本篇将讨论MPSoC中IPI的应用。首先澄清这里的IPI不是小伙伴们熟知的Vivado IPI Design Flow的IPI(IP Integrator),而是Inter-Processor Interrupt,是MPSoC中用来在异构多核系统中以中断的形式实现小批量信息交互的结构单元。

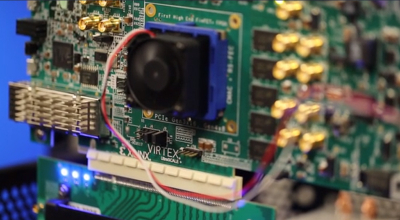

Xilinx® UltraScale™ 架构包含高性能FPGA,MPSoC和RFSoC系列,可满足广泛的系统要求,其重点是通过众多创新技术进步来降低总功耗。

PIPE 接口上的数据在 Gen3 的速度下被加密。当调试 PCIe 问题时,能在 PCIe 链接上查看各个包会很有帮助。若要实现此目的,用户需拥有协议链接分析器。由于其成本较高,能接触到此等设备的用户不多。随协议链接分析器提供的包分析工具很广泛,可对链接流量进行深入分析。

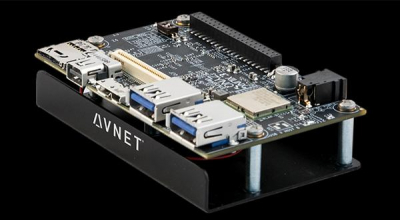

Design Automation Conference 自动设计大会是全球久负盛誉的产学研交流盛会,也是计算机学会推荐的A类会议之一。2019年第56届DAC大会在拉斯维加斯举行,Xilinx将平台升级到了支持Pynq框架的Ultra96,该平台搭载了Xilinx UltraScale+ ZU3器件。

本课程向新老设计人员介绍了 UltraScale™ 器件架构的最新内容,包括介绍全新CLB资源、时钟管理资源(MMCM 和 PLL)、全局和区域时钟资源、存储和DSP资源、源同步资源及IO接口模块特性。 同时,也阐述了如何将原有设计移植到最新UltraScale器件架构上

回顾 UltraScale 架构中的收发器增强特性。