Versal GTY 仿真:初始化、复位和速率变更

judy 在 周五, 11/04/2022 - 11:48 提交

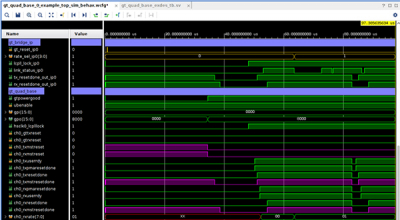

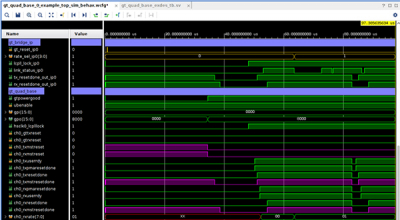

本篇博文侧重于提供 Versal™ GTY 仿真示例、演示 GTY 如何解复位以及如何执行速率变更。

本篇博文侧重于提供 Versal™ GTY 仿真示例、演示 GTY 如何解复位以及如何执行速率变更。

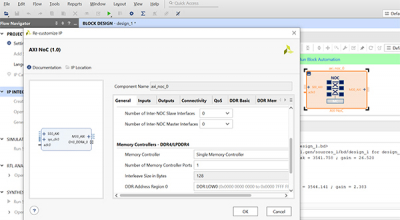

本篇博文旨在演示如何通过 NoC 从 Versal™ 应用处理单元 (APU) 访问 AXI BRAM。

了解 Versal 器件功耗估计从 XPE 迁移到 PDM 的简易迁移路径,并展示了其易用性和增强型向导。

本篇设计咨询涵盖了 Versal GTM 复位不稳定问题

AMD AI 研发团队入选的两篇论文侧重基于 Versal 异构计算平台的 AI 处理器架构设计,充分发挥 Versal 平台的算力和灵活性优势。

相较三星传统SSD固态硬盘,CPU利用率可高达97%,处理时间减少逾50%,功耗降低70%。

今天我们来介绍一下I/O planning方面的设计考虑和实现流程。

PCIe 仿真需要Endpoint 模型和Root Port 模型协同工作。用户一般可以采用购买BFM/VIP 来模拟对端模型也可以自己设计对端模型

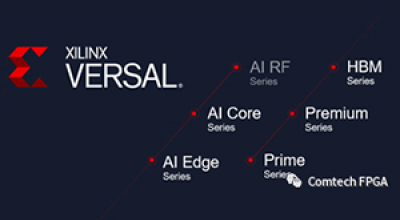

面向不同应用,Versal家族有AI Core, AI Edge , AI RF,Prime, Premium,HBM,六个系列、名字看起来是不是十分复杂?今天让我们来和您好好唠唠Versal系列这兄弟姐妹六系列!

本章旨在演示如何基于 Versal™ 来构建同时使用 SmartLynq+ 模块和高速调试端口 (HSDP) 的系统。