Versal System Monitor (Sysmon):过热告警行为

judy 在 周五, 05/05/2023 - 09:34 提交

在 CIPS GUI 中已对 Versal System Monitor 过热 (OT) 告警进行了说明

在 CIPS GUI 中已对 Versal System Monitor 过热 (OT) 告警进行了说明

要为 Versal 的多个Quad创建收发器设置,建议从 Transceiver Bridge IP 开始

通过 IP integrator 选中多个 NoC site 时,不会在整个实现过程中遵循这些约束

如果 route_design 多次运行且在硬件中不切换路径

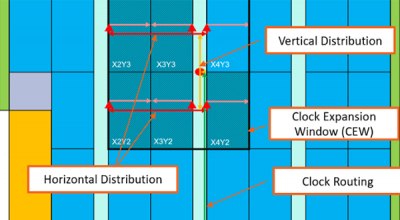

适用于 SSIT 的 Versal Fmax 取决于时钟拓扑结构扩展范围

使用“时钟校准去歪斜”时,在 Vivado 中会显示下列消息以指明是否启用该功能特性

Versal SYSMON 是通过 Vivado 中的 CIPS GUI 来配置的。您可以通过寄存器存取来对 SYSMON 进行寻址

本文将演示如何在 IP integrator 内使用 CIPS Wizard 设置“System Monitor”(系统监控器)

在Versal Advanced IO Wizard中,所包含的PLL的去歪斜电路可能导致数据速率较高时出现建立时间