基于Versal利用AXI HPC执行coherent传输

judy 在 周三, 10/18/2023 - 16:39 提交

如何使用AXI HPC端口进行CCI coherent的高速数据传输呢?

如何使用AXI HPC端口进行CCI coherent的高速数据传输呢?

本文着重介绍如何使用 Vitis™ 统一软件平台对 AIE 域进行编程。

AMD最近发布了一款专为宇宙飞行而设计的新型芯片,它叫做 the Versal™ AI Edge XQRVE23021

本文总结了Vivado 2023.1 中针对不同 Versal PCIe IP 的 10 位标签请求器功能的支持信息

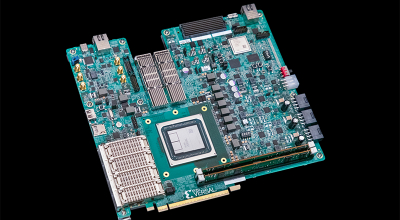

Versal HBM 器件现已投入量产,准备好为您的新一代产品提供支持

8K 摄像机的出现和更高分辨率图像的捕捉,正慢慢推动媒体工作流程的其余部分跟上 8K 内容处理的步伐

本文将继续介绍最新版本 PDM 2023.1 的新增功能

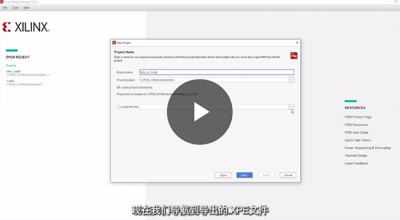

了解 Versal 器件功耗估计从 XPE 迁移到 PDM 的简易迁移路径

为了获取和传输 8K 视频,接口必须提供 4 倍于其 4K 前代产品的带宽