SWDT在Versal中的应用

judy 在 周四, 04/11/2024 - 16:25 提交

系统看门狗定时器(System WatchDog Timer)通常用于嵌入式系统,可以有效的防止软件错误、系统死锁、篡改以及意外行为

系统看门狗定时器(System WatchDog Timer)通常用于嵌入式系统,可以有效的防止软件错误、系统死锁、篡改以及意外行为

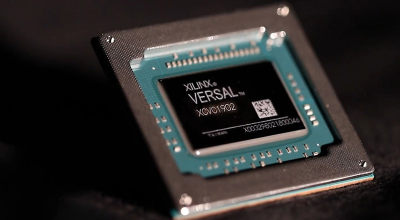

第二代 Versal 系列产品组合中首批器件借助下一代 AI 引擎将每瓦 TOPS 提升至高 3 倍,同时将基于 CPU 的标量算力较之第一代提升至高 10 倍

实验Vivado工程为“lvds_lcd”。本章介绍lvds lcd液晶屏的color bar显示。

在非常多的客户应用工程中,都会用到DDR4/LPDDR4来存取大容量数据

本实验通过PL端Verilog代码直接读写ddr4,主要了解NoC的配置方法

本文旨在探讨在 Versal 中对 eMMC 进行格式化和烧写的方法。

在本例程中,我们要做的是LED灯控制实验,每秒钟控制开发板上的LED灯翻转一次

本文介绍如何推迟XilSEM扫描功能的开始。

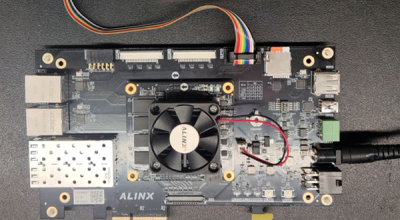

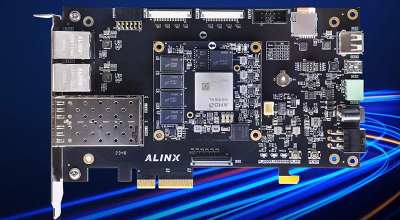

Versal 包含了 Cortex-A72 处理器和 Cortex-R5 处理器,PL 端可编程逻辑部分

Versal AI Edge VE2302器件拥有应用处理单元双核Arm Cortex-A72、实时处理单元双核Arm Cortex-R5F