一起来聊聊Versal AIE

judy 在 周三, 08/21/2024 - 10:11 提交

基于ACAP架构的Versal系列产品,在各种加速应用中,相信各位都有所了解了,作为一个异构混合加速平台,Versal结合处理器部分(A72+R5处理器)

基于ACAP架构的Versal系列产品,在各种加速应用中,相信各位都有所了解了,作为一个异构混合加速平台,Versal结合处理器部分(A72+R5处理器)

PRBS误码测试时,通常需要计算误码率。如果使用IBERT,误码率可以在Vivado的GUI界面中读取

目前在Versal上运行椭圆曲线数字签名验证的example 已经有了,请见如下源码

芯驿电子阐述了 ALINX 模块化产品设计理念,展示基于 Versal 系列芯片开发的新品及后续规划。

本文档旨在描述推荐的设计方法,帮助您在设计输入期间有效利用 AMD 的 Versal™ 自适应 SoC 资源。

AMD FPGA是电子器件中的万能芯片,在外设接口,算法指令,协议控制应用上能实现接近所有需求

该论文主要围绕着深度学习应用对密集矩阵乘法(Matrix Multiply, MM)的大量需求展开

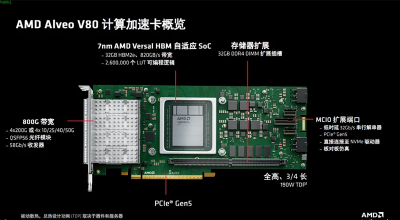

AMD Versal™ AI Core 系列和 Versal AI Edge 系列旨在凭借 AI 引擎机器学习 ( ML ) 架构来提供突破性的 AI 推断加速

Versal器件里包含多种加密引擎,包括SHA-3/384 engine、AES-GCM engine、RSA engine和ECC engine。