AI 引擎机器学习内核与计算图编程指南

judy 在 周三, 07/03/2024 - 09:42 提交

AMD Versal™ AI Core 系列和 Versal AI Edge 系列旨在凭借 AI 引擎机器学习 ( ML ) 架构来提供突破性的 AI 推断加速

AMD Versal™ AI Core 系列和 Versal AI Edge 系列旨在凭借 AI 引擎机器学习 ( ML ) 架构来提供突破性的 AI 推断加速

Versal器件里包含多种加密引擎,包括SHA-3/384 engine、AES-GCM engine、RSA engine和ECC engine。

本文将从硬件设计和驱动使用两个方面介绍基于CPM5 QDMA 的 Versal Tandem设计和 启动流程。

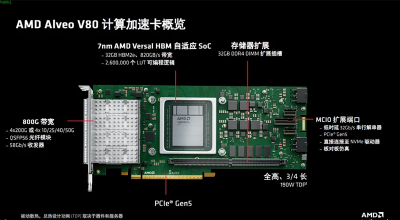

Alveo V80 的逻辑密度至高翻倍、存储器带宽至高翻倍且网络带宽可高至 4 倍,可以实现强大的计算集群,同时还能优化卡、服务器数量以及机架空间。

本文可让开发者们看懂 AMD Vivado™ Design Tool 2023.2 中的“AMD Versal™ Adaptive SoC CPM PCIE PIO EP 设计”CED 示例。

开发板有两路千兆以太网,通过RGMII接口连接,本实验演示如何使用Vitis自带的LWIP模板进行PS端千兆以太网TCP通信。

本章使用一个简单的串口打印来体验一下Vivado Vitis和PS端的特性

AI 驱动型系统正催生指数级算力需求,使得在紧凑的空间和功率限制内设计嵌入式应用变得更具挑战性。设计人员需要支持嵌入式 AI 系统中的所有计算阶段

使用IBERT测试误码率和眼图必须有个收发环通的硬件,开发板上有2个SFP光纤接口,本实验把2个光接口收发两两连接,形成2个收发环通链路。