AMD Versal FPGA技术加持 打开电力电子仿真技术新未来

judy 在 周四, 02/29/2024 - 15:00 提交

摆脱传统多FPGA解耦技术的束缚,在单块FPGA资源中支持更大规模的复杂电力电子电路模型

摆脱传统多FPGA解耦技术的束缚,在单块FPGA资源中支持更大规模的复杂电力电子电路模型

不同厂商的MSI-X结构所在配置空间的位置不同

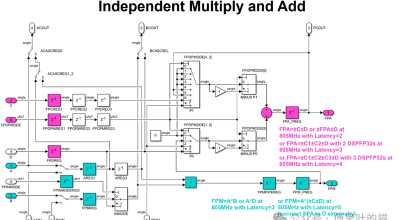

本文将重点介绍其中的DSPFP32,它是一个硬化的浮点加法器和乘法器

通过本视频了解套件的功能、配件以及如何启用该套件进行设计

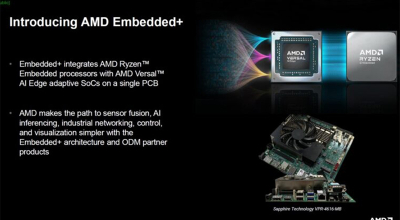

AMD最新宣布推出的嵌入式增强版(Embedded Plus)带来了令人振奋的技术进步

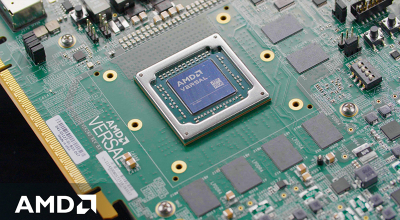

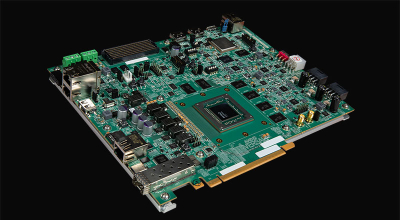

VEK280 评估套件是一款基于 Versal AI Edge 系列 VE2802 器件的全新评估平台

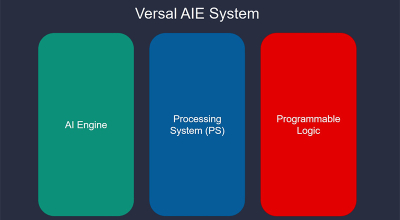

本文将演示在这 3 个不同域上运行的完整系统示例

全新 AMD DisplayPort 2.1 子系统支持 AMD UltraScale+ FPGA 和 Versal 架构接收

本文档旨在描述推荐的设计方法,帮助您以 AMD Versal™ 器件为目标,满足设计收敛期间的性能目标。