借助第二代 AMD VERSAL 实现先进医疗成像

judy 在 周三, 12/04/2024 - 09:33 提交

第二代 Versal™ 自适应 SoC 配备的处理系统可提供比前代至高多出 10 倍的标量算力性能,同时支持 DDR5 内存

第二代 Versal™ 自适应 SoC 配备的处理系统可提供比前代至高多出 10 倍的标量算力性能,同时支持 DDR5 内存

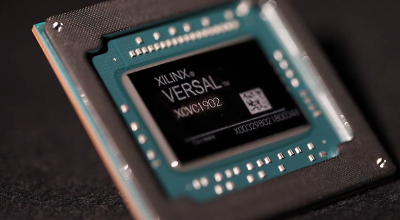

Versal的一个GTM Quad包含4路channel和两个LCPLL。本文中的办法就是展示如何在设计里面实现此种配置的自动化。

环回(loopback)是GT的一种特殊配置模式。可以把发送端的数据直通过自身PMA层或对方器件(不加进一步处理)后再转回给发送器件的接收端

Versal CPM QDMA EP Design 默认状态下的Setup Debug流程及debug core 时钟,以Vivado 2024.1为例

我们在Versal上开发驱动程序的时候,经常会访问某些硬件寄存器,读取或者写入某个值

本文以国内用户群体最多的Versal AI Edge VE2302为例,分享一些实际工程设计的细节和经验。

在Vesal器件的DDRMC DDR4/LPDDR4接口上,控制器的系统时钟源通常是由片外的差分时钟所提供的

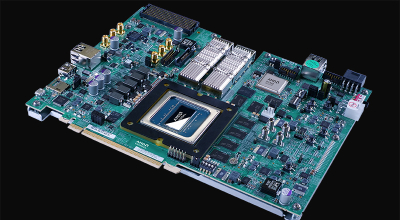

AMD Alveo V80加速器卡基于7nm Versal™自适应SoC架构,采用AMD Versal高带宽内存 (HBM) 器件,提供速度高达820GB/s的4x200G网络

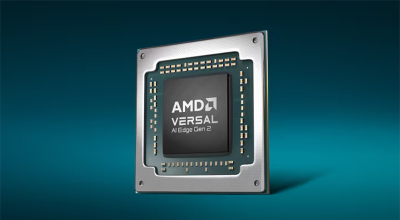

第二代 AMD Versal™ AI Edge 系列自适应 SoC 采用高度集成的架构设计。与前代相比,该处理系统可提供至高10 倍的标量算力性能

第二代 Versal™ AI Edge 系列自适应 SoC 旨在通过增强的处理器系统、功耗优化的下一代 AI 引擎以及 AMD 全球领先的可编程逻辑来提升 AI 驱动型应用的系统级性能