FPGA 大神 Adam Taylor 使用 ChipScope 调试 AMD Versal 设计

judy 在 周五, 05/16/2025 - 16:37 提交

在上篇文章中,我们已经通过测试图案生成器,成功验证了 ALINX VD100 的图像显示链路。这次终于要接入 MIPI 摄像头,进行真正的图像处理了!

在上篇文章中,我们已经通过测试图案生成器,成功验证了 ALINX VD100 的图像显示链路。这次终于要接入 MIPI 摄像头,进行真正的图像处理了!

AMD Versal自适应 SoC 架构通过异构加速和硬 IP集成提供卓越的系统性能功耗比。但当开发者想从上一代 FPGA 迁移时如何确保最佳结果呢?

本篇博文主要讲解在 PL 中将来自 IP 核的超 32 次中断布线到 PS 的情况下,该如何使用 AXI Interrupt Controller (INTC) 中的级联模式。

3D重建通过精确捕捉物体表面几何信息,构建出高精度数字模型,在多个行业中获得了广泛应用。从工业制造、航空航天,到文物保护、建筑工程等领域

本文将探讨优化数据传输、AI 引擎加速以及动态功能交换(DFX)的关键技术,以全面释放 AMD Versal SoC 的潜能。

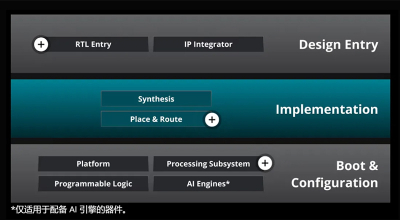

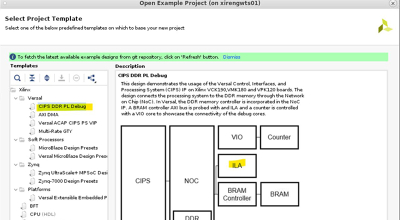

Vivado 设计套件提供经过优化的设计流程,让传统 FPGA 开发人员能够加快完成 Versal 自适应 SoC 设计。

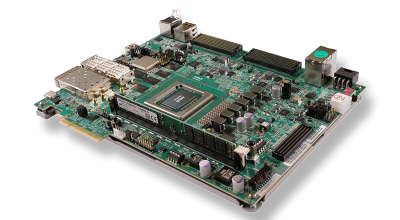

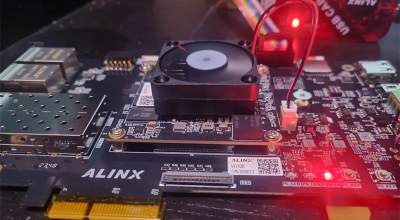

这是一块基于 AMD Versal Edge AI 平台的开发板,功能特别强大,可以用来做图像处理、人工智能等各种高阶应用。

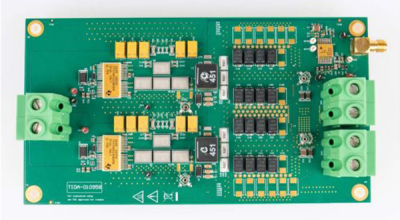

TIDA-010958 是一种面向 AMD® Versal® AI Core XQRVC1902 内核电源轨的耐辐射同步降压电源参考 设计。此设计非常适用于 12V 输入操作,可生成 0.8V 的输出电压和最大 80A 的输出电流

我们将使用 Clocking Wizard 文档 PG321 中的“通过 AXI4-Lite 进行动态重配置的示例”章节作为参考。

了解 AMD Versal 产品组合与前几代 FPGA 相比在时钟架构功能的增强,并了解如何利用 AMD Vivado™ 工具的先进功能快速完成设计并实现性能目标。