适用于 AMD Versal™ 自适应 SoC 的 Vivado™ Design Suite

judy 在 周五, 03/21/2025 - 09:34 提交

AMD Vivado™ Design Suite 实现突破性优化,可显著加快 Versal™ 自适应 SoC 硬件设计工作,与此同时大大简化了从旧架构到新架构的迁移

AMD Vivado™ Design Suite 实现突破性优化,可显著加快 Versal™ 自适应 SoC 硬件设计工作,与此同时大大简化了从旧架构到新架构的迁移

该系统可充分利用现有的HAPS-100生态系统,并支持混合的HAPS-200/100系统设置,可从单FPGA设置扩展到容量高达108亿门的多机架设置。

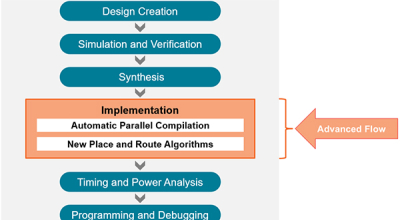

本文介绍了 Versal 的Advanced Flow,这是 Vivado 2024.2 版本提供的一套新的布局布线功能。

PRBS(pseudorandom binary sequence) Pattern包括PRBS-[7/9/15/31],可以用作不同的协议或者场景

第二代 AMD Versal AI Edge 系列自适应 SoC 的异构架构允许使用单芯片解决方案处理自动驾驶系统的所有阶段 —— 检测、感知、规划和执行

新一代高性能数字信号处理(DSP)应用日益增长的计算需求,正迅速接近传统FPGA架构的资源和功耗上限。您知道吗?借助AMD Versal™ AI Engine ,您能够......

Versal器件上DDR4硬核控制器DDRMC跑仿真时,按照IP的默认设置,在IP wizard中使能了“Internal Responder”

本文将通过PMC_GPIO作为例子来描述如何唤醒Versal系统。

第二代 Versal™ 自适应 SoC 配备的处理系统可提供比前代至高多出 10 倍的标量算力性能,同时支持 DDR5 内存

Versal的一个GTM Quad包含4路channel和两个LCPLL。本文中的办法就是展示如何在设计里面实现此种配置的自动化。