嵌入式软件与生态系统:为嵌入式开发者提供必要的组件

demi 在 周六, 10/12/2019 - 09:50 提交

Xilinx 及其联盟成员提供嵌入式工具与运行时环境可帮助您高效快速地将概念转化为生产。我们可为您提供使用 Xilinx Zynq® SoC 和 Zync UltraScale+ MPSoC 器件、MicroBlaze™ 处理器内核和 Arm Cortex-M1/M3 微控制器创建嵌入式系统所需的所有组件,包括开源操作系统和裸机驱动程序、多运行时和......

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

Xilinx 及其联盟成员提供嵌入式工具与运行时环境可帮助您高效快速地将概念转化为生产。我们可为您提供使用 Xilinx Zynq® SoC 和 Zync UltraScale+ MPSoC 器件、MicroBlaze™ 处理器内核和 Arm Cortex-M1/M3 微控制器创建嵌入式系统所需的所有组件,包括开源操作系统和裸机驱动程序、多运行时和......

众所周知,我们可以通过索引值(或称下标)来查找序列类型(如字符串、列表、元组…)中的单个元素,那么,如果要获取一个索引区间的元素该怎么办呢?

Vitis™ 统一软件平台包括一组广泛的、性能优化的开源库,这些库提供了即开即用的加速功能,并且对现有应用实现最小化代码更改或零更改。

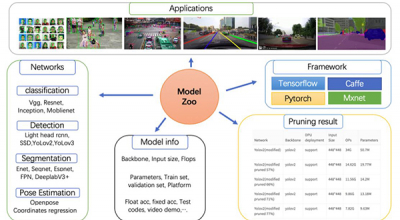

Vitis™ AI 是 Xilinx 的开发平台,适用于在 Xilinx 硬件平台(包括边缘设备和 Alveo 卡)上进行人工智能推断。它由优化的 IP、工具、库、模型和示例设计组成。Vitis AI 以高效易用为设计理念,可在 Xilinx FPGA 和 ACAP 上充分发挥人工智能加速的潜力。

在“设置”对话框的“约束”部分下,选择“默认约束设置”作为活动约束设置;包含在Xilinx设计约束(XDC)文件中捕获的设计约束的一组文件,可以将其应用于设计中。

Vitis 统一软件平台包括:全面的内核开发套件,可无缝构建加速的应用;完整的硬件加速开源库,针对 Xilinx 硬件平台进行了优化;插入特定领域的开发环境,可直接在熟悉的更高层次框架中进行开发;不断发展的硬件加速合作伙伴库和预建应用生态系统。

首先来理清楚MIO与EMIO的关系。MIO是PS的I/O引脚,一共有54个,分为Bank0与Bank1,可以接许多外设比如UART、SPI或GPIO等,另外可以引脚复用。

FPGA是可编程芯片,因此FPGA的设计方法包括硬件设计和软件设计两部分。硬件包括FPGA芯片电路、 存储器、输入输出接口电路以及其他设备,软件即是相应的HDL程序以及最新才流行的嵌入式C程序。

如果将计算机比作人的话,CPU就是人的大脑,而PCIe就是人的神经中枢,负责内部数据信息的传输。

PCI,英文全称:PeripheralComponent Interconnect,外围组件互联,由Intel于1991年提出。随着Intel Pentium处理器诞生而迅速发展,当时几乎所有的外围设备,从硬盘控制器、声卡、显卡和网卡,都使用PCI插槽来连接到计算机的主板上。