PCIx系列之“M-PCIe”

demi 在 周三, 09/25/2019 - 13:40 提交

M-PCIe即Mobile PCIe,主要应用对象是智能手机等嵌入式设备。PCI-SIG在PCIe Spec V3.1中引入基于MIPI M-PHY V2.0的M-PCIe。相比于标准的PCIe总线,M-PCIe ECN主要的改动在物理层,通过引入M-PHY,旨在获得更低的功耗以适应嵌入式设备的低功耗要求。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

M-PCIe即Mobile PCIe,主要应用对象是智能手机等嵌入式设备。PCI-SIG在PCIe Spec V3.1中引入基于MIPI M-PHY V2.0的M-PCIe。相比于标准的PCIe总线,M-PCIe ECN主要的改动在物理层,通过引入M-PHY,旨在获得更低的功耗以适应嵌入式设备的低功耗要求。

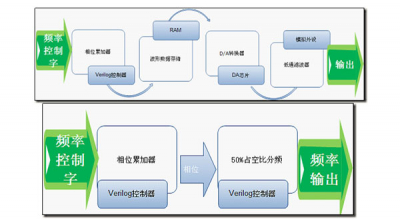

在大部分的教科书中,都会提到如何分频,包括奇数分频,偶数分频,小数分频等。首先讲述DSS(直接频率合成法)的原理。DDS是重要的频率合成方法,在波形发生器中有极其重要的应用。DDS主要由几部分组成:a) 相位累加器;b) RAM数据读取;c) D/A转换器;d) 低通滤波器。

根据维基百科定义:字符串是由零个或多个字符组成的有限序列。而在Python 3中,它有着更明确的意思:字符串是由Unicode码点组成的不可变序列(Strings are immutable sequences of Unicode code points.)

我们知道xilinx FPGA的selectio中有ilogic和ologic资源,可以实现iddr/oddr,idelay和odelay等功能。刚入门时可能对xilinx的原语不太熟练,在vivado的tools-> language templates中搜索iddr idelay等关键词,可以看到A7等器件下原语模板。复制出来照葫芦画瓢,再仿真一下基本就能学会怎么用了。

在ZYNQ进阶之路3中我们讲解了PL端UART 发送的设计,本节我们讲解PL端实现串口UART的接收设计。

发起沿和捕获沿(Launch edge & Capture edge)

上周的PyCoder's Weekly上分享了一篇小文章,它里面提到的冷知识很有意思,作者稍作补充,分享给大家。它提到的部分问题,读者们可以先思考下:若两个元组相等,即 a==b 且 a is b,那么相同索引的元素(如a[0] 、b[0])是否必然相等?若两个对象的 hash 结果相等,即 hash(a) == hash(b),那么它们是否必然相等呢?

在ZYNQ进阶之路2中我们讲解了PL端PWM呼吸灯的设计,本节我们讲解PL端实现串口UART的发送设计。

时序不满足约束,会导致以下问题:编译时间长的令人绝望;运行结果靠运气——时对时错。

连续赋值语句是Verilog数据流建模的基本语句,用于对线网进行赋值,等价于门级描述,是从更高的抽象角度来对电路进行描述。连续赋值语句必须以关键词assign开始。