Xilinx zynqMP开发基本步骤

demi 在 周二, 09/10/2019 - 11:21 提交

使用Vivado 工具生成 .hdf文件,比如ZU9_cpu.hdf;使用SDK工具生成FSBL。FSBL的作用主要是初始化PLL,DDR,MIO管脚分配,烧写FPGA,运行uboot等。核心代码代码位于psu_init.c中。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

使用Vivado 工具生成 .hdf文件,比如ZU9_cpu.hdf;使用SDK工具生成FSBL。FSBL的作用主要是初始化PLL,DDR,MIO管脚分配,烧写FPGA,运行uboot等。核心代码代码位于psu_init.c中。

今天,我们聊聊双核通信。双核通信的基础是已经建立好了双核工程,且配置完成。两个CPU之间传递数据,采用了共享内存,共享内存设置在OCM(On Chip Memory)内。

典型的时序模型由发起寄存器、组合逻辑和捕获寄存器3部分组成,如图1所示形成了三条时钟路径:原时钟路径(Source Clock path)、数据时钟路径(Data path)、目的时钟路径(Destination Clock path)。

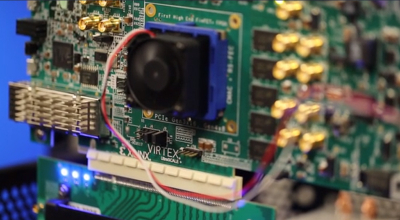

DDR对于做项目来说,是必不可少的。一般用于数据缓存和平滑带宽。今天介绍下Xilinx DDR控制器MIG IP核的例化及仿真。

话不多说,进入今天的主题:生成zynq裸核启动文件。1、首先在vivado SDK中分别建立两个工程;2、配置Core1即从核中的BSP文件;3.配置Core0和Core1的DDR空间分配;4.建立FSBL文件,并配置main()文件;5.生成mcs文件和烧写mcs文件到QSPI Flash;6.完成操作将.MCS文件烧写进板子里

Python 中的sys模块极为基础而重要,它主要提供了一些给解释器使用(或由它维护)的变量,以及一些与解释器强交互的函数。本文将会频繁地使用该模块的getsizeof()方法。

PIPE 接口上的数据在 Gen3 的速度下被加密。当调试 PCIe 问题时,能在 PCIe 链接上查看各个包会很有帮助。若要实现此目的,用户需拥有协议链接分析器。由于其成本较高,能接触到此等设备的用户不多。随协议链接分析器提供的包分析工具很广泛,可对链接流量进行深入分析。

部分硬件设计中需要CPU完成对电路寄存器的配置,为了完成Zedboard对FPGA上部分寄存器的配置功能,可以在PS单元(处理器系统)上运行裸机程序(无操作系统支持)完成和PL单元(FPGA部分)的数据交互功能,此时PS单元更像单片机开发;另一种方法是PS单元运行Linux操作系统,通过驱动程序和应用程序......

在这篇文章里你可以了解到广告推荐算法Wide and deep模型的相关知识和搭建方法,还能了解到模型优化和评估的方式。我还为你准备了将模型部署到赛灵思 FPGA上做硬件加速的方法,希望对你有帮助。阅读这篇文章你可能需要20分钟的时间。