基于FPGA的intoPIX 8K TicoXS FIP编解码器IP助力定制化视频处理应用

judy 在 周四, 08/01/2024 - 17:27 提交

全新JPEG XS ISO标准定义了一种实现高质量视频传输的压缩技术。基于Agilex™ FPGA,联合intoPIX合作开发了一个完整的评估平台

全新JPEG XS ISO标准定义了一种实现高质量视频传输的压缩技术。基于Agilex™ FPGA,联合intoPIX合作开发了一个完整的评估平台

HOLOPLOT 音响系统可以精准地将不同音频内容传送到观众席的不同位置,让听众踏上一段独特而变化万千的声音体验之旅。

在本次研讨会中,您将了解到 AMD 在 FPGA 和 SoC 产品上的独特价值以及几十年来在关键任务领域的成功经验。

本篇文章是SmartDV数字芯片设计经验分享系列文章的第二篇,将继续分享第二到第四主题,包括FPGA原型的基本概念、常见挑战和基本调整

AMD公布2024财年第二季度财报。第二季度,AMD营收58.35亿美元,同比增长9%,环比增长7%

AMD 自适应计算峰会在深圳举行,聚焦 AMD 自适应 SoC 和 FPGA 产品最新动态,以及设计工具和开发环境的前沿技巧

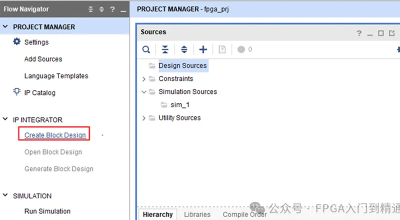

本文将详细介绍Vivado Block Design的使用流程,旨在帮助读者从基础到高级技巧,全面掌握这一工具。

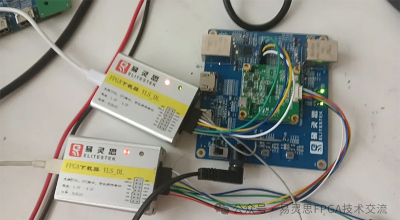

有客户认为Ti60F100内部flash容量比较小,只有16Mb,需要外挂flash.这里我们提供了内部flash和外部flash分别操作的方案

从Vivado 2024.1开始,为了能帮助用户更直观地了解Versal DFX设计的状况,新支持了一条命令report_dfx_summary。下面我们就一起来了解一下这条命令的详情。

EPS-VU13P-19EG-QSFP28 FPGA板卡配备32 个 QSFP28 光接口,支持超高带宽的数据传输,能够满足 5G 乃至未来 6G 通信对高速数据传输和处理的严苛要求