AMD MPSoC PS PCIe 访问PL BRAM的参考设计

judy 在 周四, 07/18/2024 - 17:25 提交

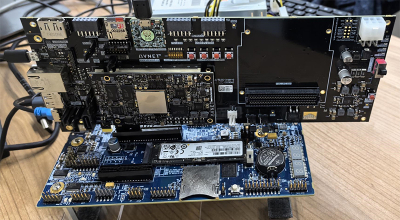

客户要求AMD MPSoC 的 PS 部分的 PCIe 能访问 PL的AXI BRAM。从Avnet 借了 UltraZed Board,得到了Vivado工程。

客户要求AMD MPSoC 的 PS 部分的 PCIe 能访问 PL的AXI BRAM。从Avnet 借了 UltraZed Board,得到了Vivado工程。

十多年后的今天,劳伦斯利弗莫尔国家实验室的“El Capitan”超级计算机即将成为世界上最强大的(已知)超级计算机

在本教程中,我们将介绍使用 FPGA 实现深度学习的技术,深度学习是近年来人工智能领域的热门话题。

FPGA常见面试题总结

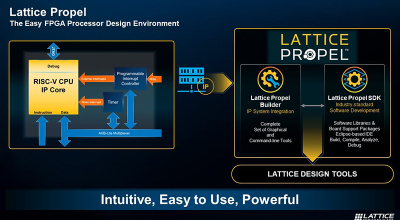

许多嵌入式系统的开发者都对使用基于FPGA的SoC系统感兴趣,但是基于传统HDL硬件描述语言的FPGA开发工具和复杂流程往往会令他们望而却步

本文汇总了可编程逻辑器件适航标准-DO254 VHDL编码规范

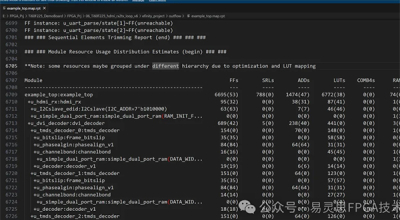

在outflow <project>.map是网表对FPGA资源的映射。比如gbuf,dspt等原语的是怎样适配的

本文将详细介绍FPGA时钟设计的概念、技巧和优化策略。

AMD FPGA是电子器件中的万能芯片,在外设接口,算法指令,协议控制应用上能实现接近所有需求

在上周 AMD 的技术日上,AMD 披露了有关 Zen 5 的一些技术细节,其中还涵盖了 Ryzen AI 300 和 Ryzen 9000 系列的一些关键元素。