开放架构破局eFPGA困境,Zero ASIC Platypus要做下一个RISC-V?

judy 在 周五, 05/09/2025 - 10:58 提交

在芯片设计的周期与寿命愈发错位的当下,如何应对“技术演进快、基础设施更迭慢”的结构性矛盾,成为整个半导体行业绕不开的问题

在芯片设计的周期与寿命愈发错位的当下,如何应对“技术演进快、基础设施更迭慢”的结构性矛盾,成为整个半导体行业绕不开的问题

本文将探讨优化数据传输、AI 引擎加速以及动态功能交换(DFX)的关键技术,以全面释放 AMD Versal SoC 的潜能。

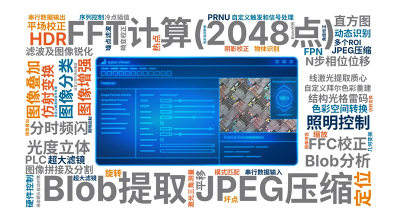

在工业检测领域,毫秒级的处理延迟可能意味着良率波动或产能损失。传统CPU架构受限于串行计算与数据传输瓶颈,而FPGA的并行计算能力正在打开实时图像处理的新维度。

eSPI总线具有低功耗、管脚数量少、高效的数据传输等优点,常用于与EC、BMC、SIO等外设的通信,是PC中CPU与这些外设通信的主流协议

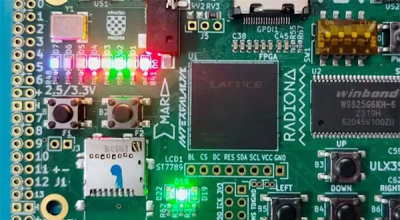

今天就介绍一个使用开源工具链来开发FPGA的方式。本文核心:开源 FPGA 工具链,例如 APIO、IceStrom、yosys OssCAD 等使用。

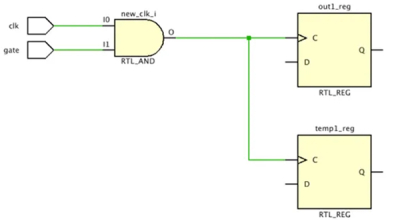

传统上,使用门控时钟是 ASIC 设计中降低系统功耗的常见方法。通过门控时钟,可在非必要时阻止整组寄存器的状态转换。

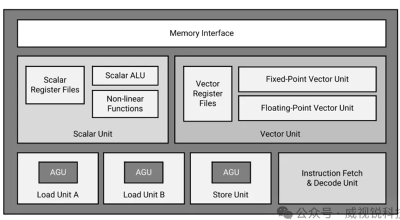

AI Engine是一款高度优化的处理器,具有单指令多数据(SIMD)和超长指令字(VLIW)处理器,支持定点和浮点精度。

AMD QDMA Subsystem for PCI Express( PCIe® )旨在利用多队列的概念实现高性能 DMA,以搭配 PCI Express® Integrated Block 一起使用

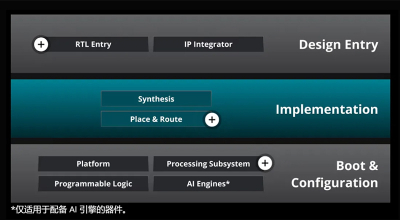

Vivado 设计套件提供经过优化的设计流程,让传统 FPGA 开发人员能够加快完成 Versal 自适应 SoC 设计。