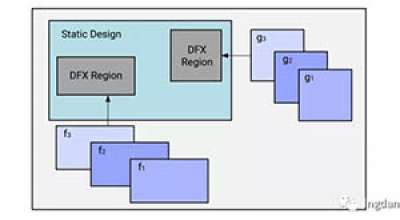

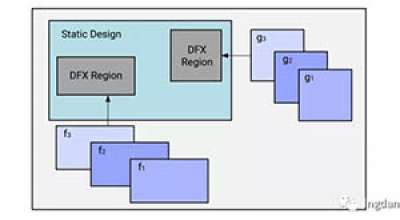

面向Abstract shell的DFX

judy 在 周二, 11/30/2021 - 14:57 提交

使用 DFX 有助于设计者转而采用更少或更小的器件,降低功耗并提高系统升级能力。随时按需加载功能,更有效利用芯片。

使用 DFX 有助于设计者转而采用更少或更小的器件,降低功耗并提高系统升级能力。随时按需加载功能,更有效利用芯片。

就在边缘设备上部署解决方案而言,硬件必须拥有充足的算力,才能处理ML算法工作负载。人们可以使用各种深度学习处理单元(DPU)配置对Kria K26 SOM进行配置,还能根据性能要求,将最适用的配置整合到设计内。

本白皮书描述了推荐的设计方法,以实现对 Xilinx® FPGA 器件资源的有效利用,并在 Vivado® 设计套件中更快地实现设计和时序收敛。提供了推荐方法背后的原因,以支持和实现明智的设计决策。

此次研讨会,将会为大家介绍Xilinx RFSoC系列器件主要特性与优势,并针对其独特的架构做详细讲解。除Xilinx RFSoC解决方案之外,本次会议将对5G 毫米波/软件无线电系统应用及解决方案进行介绍及讲解。

已注册并登录 Xilinx 产品许可证站点,在尝试下载 Xilinx 工具的时候,偶尔会弹出一条 “出口合规警示” 的提示消息。这条消息代表了什么?该如何操作才能继续下载?

Kria™ SOM自适应系统模块是一种量产型小尺寸嵌入式板卡,拥有完整的软件堆栈与预构建的量产级加速应用,可快速部署各种各样的边缘应用。

对FPGA进行上板调试时,使用最多的是SignalTap,但SignalTap主要用来抓取信号时序,当需要发送信号到FPGA时,Jtag Master可以发挥很好的作用,可以通过Jtag Master对FPGA进行读写测试

FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者原语的方式来进行乘法操作。在里面可以设置有符号还是无符号数乘法。

本指南详细介绍Vivado®工具中Tcl脚本的使用,查询和修改内存设计的自定义流程。讨论了使用Tcl程序来定义和共享自定义命令。

在STA中,要分析上游器件和FPGA之间的时序关系就得指定input delay。