Vivado中怎么做set_input_delay约束

guanxiao_505740 在 周五, 11/26/2021 - 11:18 提交

在STA中,要分析上游器件和FPGA之间的时序关系就得指定input delay。

在STA中,要分析上游器件和FPGA之间的时序关系就得指定input delay。

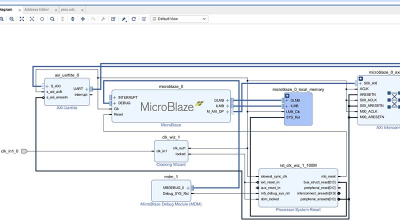

本文以浮点数Floating-point IP核将定点数转换为浮点数为例,详细讲解AXI DMA IP核的使用方法。

我在 Vivado 中有个 VHDL 项目。 UG900 用户指南指出: “后综合和后实现时序仿真仅就 Verilog 提供支持。不支持 VHDL 时序仿真。” 这是否意味着我不能在 VHDL 项目中运行时序仿真? 该项目有没有运行时序仿真的办法?

本篇简介教程演示了如何共享并访问位于远程实验室内的开发板或归其它同事所有的开发板。

这些实践旨在为用户提供快速入门指导,帮助其简要了解工具流程原理。我们选择了一项非常简单的设计,便于读者理解流程中的不同步骤。

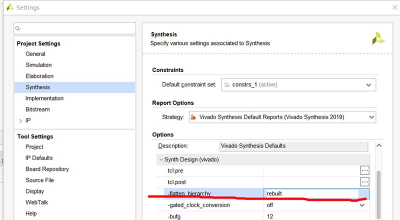

当选择为none,综合器优化的最少,当选择为full时,综合器优化的最多,选择rebuilt时,工具自动选择一个折中的方案,对当前工程做优化。如果在rebuilt的选项不希望一些信号被优化,则可以调用原语进行约束。

智能互联设备变得越来越普及,目前全球已经部署了数十亿台智能互联设备。这些智能设备存在于我们的手机、平板电脑、手表、家庭、汽车、城市和云端。在过去,智能设备是指有微控制器,运行某个软件的设备,如今的智能设备则需要执行类人任务。

借助赛灵思Alveo U30媒体加速器卡,亚马逊网络服务(AWS)EC2 VT1实例不仅可加速实时转码,还显著降低了直播视频流的转码成本,从而为高达4K超高清分辨率的多流视频转码提供了最佳性价比。

赛灵思亚太区资深战略应用工程师高亚军将为大家讲解Vivado设计套件,分享其在使用过程中的技巧和设计方法论。

Xilinx Vitis 2020.1里面运行C程序时提示找不到microblaze_0