All node

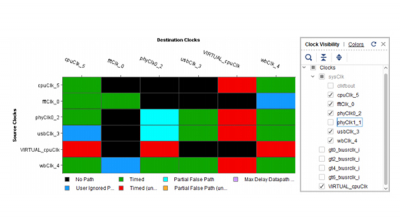

Vivado Design Suite 用户指南:设计分析与收敛技巧 (中文版) (v2019.2)

judy 在 周一, 10/12/2020 - 09:57 提交

本手册详细介绍 Vivado工具的功能特色,包括 FPGA 设计的逻辑和时序分析以及工具生成的报告和消息。探讨达成时序收敛的方法,包括审查时钟树和时序约束、设计布局规划以及实现运行时间与设计结果的平衡。

AXI_lite代码简解-AXI-Lite 源码分析

judy 在 周一, 10/12/2020 - 09:40 提交

对于使用AXI总线,最开始肯定要了解顶层接口定义,这样才能针对顶层接口进行调用和例化,打开axi_lite_v1_0.v文件,第一段就是顶层的接口定义:

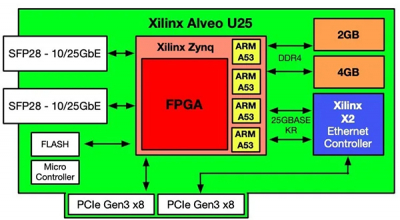

SmartNIC 与普通的 NIC 有哪些显著性差异?

judy 在 周六, 10/10/2020 - 11:35 提交

普通 NIC 定位于高效迁移服务器的网络数据包,通常包括不同程度的为优化性能而设计的传统卸载。SmartNIC 整合了多方面的附加计算资源,但是这些架构就像雪花一样各不相同,因此,我们将深入研究规模最大、最受欢迎的供应商所提供的几种方法。

AXI_lite代码简解-查看源码

judy 在 周六, 10/10/2020 - 10:36 提交

要看到AXI-Lite的源码,我们先要自定义一个AXI-Lite的IP,新建工程之后,选择,菜单栏->Tools->Creat and Package IP

给我一颗 FPGA,可以撬起所有显示的接口和面板

judy 在 周六, 10/10/2020 - 09:49 提交

作为FPGA的发明者——赛灵思,手握极具灵活性、高性能的FPGA技术,似乎看别的芯片都有一种嫌弃不够畅快的感觉。当瞄上显示领域时,就会发出来自心底的一问:“一个FPGA就能解决的事,为什么要那么多ASIC/ASSP?”

PYNQ框架下的快速分形图形实现

judy 在 周六, 10/10/2020 - 09:29 提交

Fractal(分形图形),是由IBM研究室的数学家曼德布洛特(Benoit.Mandelbrot,1924-2010)提出的,其维度并非整数的几何图形,而是在越来越细微的尺度上不断自我重复,是一项研究不规则性的科学。下面是一个最简单的例子,首先画一条线段,然后把它平分成三段,将中间那一段用一个等边三角形的两条边代替

还原最真实的世界,FPGA是怎么做到的?

judy 在 周五, 10/09/2020 - 15:03 提交

自从影像记录诞生以来,还原逼真世界的每一寸细节一直便是行业的终极追求。影响图像质量包括分辨率、位深度、帧速率、色域、亮度五个要素,近年来4K/8K 60Hz/120Hz的显示面板逐渐被人耳熟能详,伴随着分辨率、位深度、帧速率升级,色域和亮度也被提出新的要求

打造面向未来的新一代技术, Virtex UltraScale+ VU19P 批量发货了!

judy 在 周五, 10/09/2020 - 11:44 提交

您准备开发面向未来的最复杂、最具创新水平的未来新技术吗?我们能帮助您实现愿望。 今天,我们很荣幸地宣布,赛灵思最大的 FPGA,即 Virtex UltraScale+ VU19P 现已普遍供货并已批量付运众多客户。

Vivado Design Suite 用户指南:采用 IP 进行设计 (中文版) (v2020.1)

judy 在 周五, 10/09/2020 - 09:37 提交

本文描述如何使用 Vivado工具将来自赛灵思 IP 目录的即插即用 IP 模块(包括自定义封装的 IP)添加到您的设计中,并描述如何在设计中使用 IP、创建所需输出文件、管理和升级 IP 以及利用 IP 对设计进行仿真。