AXI总线详解-不同类型的DMA

judy 在 周三, 09/23/2020 - 09:33 提交

几个常用的 AXI 接口 IP 的功能(上面已经提到):

AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换

AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GP<----->AXI-Stream 的转换

几个常用的 AXI 接口 IP 的功能(上面已经提到):

AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换

AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GP<----->AXI-Stream 的转换

本应用说明提供了一个包含控制逻辑的模块,用于将SMPTE UHD-SDI与UltraScale™ GTH收发器耦合,形成一个完整的UHD-SDI接口。本应用说明还提供了一个在Xilinx UltraScale FPGA KCU105评估板上运行的SDI设计示例。

欢迎参观慕尼黑华南电子展蓝牙世界专区,聆听蓝牙生态峰会演讲

时间:2020年11月3日

地点:深圳宝安国际会展中心 10号馆 10C59展位/论坛区

背景:

Gemalto 的生物识别技术与基于 FPGA 的匹配引擎相结合,具有速度、成本降低、高能效、 可扩展性和灵活性方面的独特优势。

在ZYNQ的体系结构中定时器太丰富了,而大量的教程中基本就只玩了私有定时器,可以中断就OK了。其实在ZYNQ中定时器资源很丰富,每个CPU有自己的私有定时器和看门狗,有一个所有CPU共享的全局定时器和看门狗,两个三路定时器还有AXI_TIMER的IP可用,不过好像很少有博客把这些测试完。

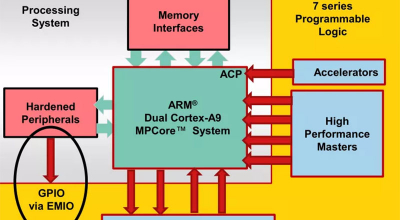

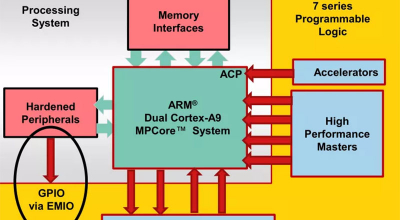

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI-Lite或AXI4转接。PS与PL之间的物理接口有9个,包括4个AXI-GP接口和4个AXI-HP接口、1个AXI-ACP接口

这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用很简单的程序就可以进行DDR3的测试。

本设计使用Ultra96开发板,使用InceptionV3网络,以及Vitis-AI的量化编译工具链,制作了一个五花分类装置。利用Xilinx的DPU(Deep learning Processing Unit)IP,Vitis-AI工具链,快速的在FPGA上部署深度学习网络。

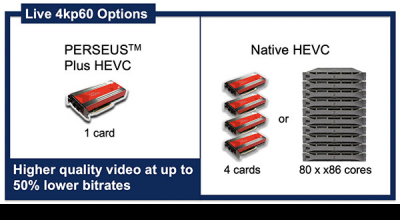

V-Nova LCEVC 是一项独特的视频编码技术,可显著提高任何标准编码器的质量和吞吐量。与 Xilinx FPGA 结合使用时,PERSEUS 可提供市场上密度最高的编码解决方案

安富利日前推出了96Boards ON Semiconductor双摄像头夹层卡开发和原型创建平台。该平台适用于与双摄像头模块搭配使用的AP1302图像处理器,能够帮助设计和系统工程师利用行业标准技术创建经济、高效的嵌入式视觉应用。