XILINX ZYNQ7100 的上电顺序

guanxiao_505740 在 周二, 09/08/2020 - 15:44 提交

建议的上电顺序为VCCPINT,然后是VCCPAUX和VCCPLL,然后PS VCCO提供(VCCO_MIO0,VCCO_MIO1和VCCO_DDR)以实现最小电流消耗并确保I / O上电时为3态。在上电序列中,要求将PS_POR_B输入置为GND。直到VCCPINT,VCCPAUX和VCCO_MIO0达到最低操作级别,才能确保PS eFUSE完整性

建议的上电顺序为VCCPINT,然后是VCCPAUX和VCCPLL,然后PS VCCO提供(VCCO_MIO0,VCCO_MIO1和VCCO_DDR)以实现最小电流消耗并确保I / O上电时为3态。在上电序列中,要求将PS_POR_B输入置为GND。直到VCCPINT,VCCPAUX和VCCO_MIO0达到最低操作级别,才能确保PS eFUSE完整性

本次网络研讨会描述了两个使用 Zynq UltraScale + RFSoC 进行无线通信的设计示例。 首先,让我们回顾一下针对大规模 MIMO(64x64),100MHz LTE(ORAN 7.2 split)的设计,并解释其实现和选型性能数据。

客户收到新买的ZCU106,运行Xilinx的linux正常。使用的Xilinx SDK 2018.3调试自己创建的helloworld时却出现异常,程序跑飞。在Vitis 2020.1下创建的helloworld后,使用psu_init初始化,也出现程序跑飞的情况。

Xilinx 和 Hewlett Packard Enterprise(HPE)建立了最终用户解决方案,该解决方案使用 HPE ProLiant DL385 Gen10 Plus 服务器和第二代 AMD EPYC 处理器实现革命性的性能。

日常拍照时,我们有时会遇到拍出来的照片失焦的情况。如果拍下的瞬间比较难得,这样的情况就更加可惜了。但是,利用FPGA进行编程,这些照片可能还能”拯救一下“!今天,小编为大家带来暑期学校优秀项目之失焦图像去模糊系统的分享。

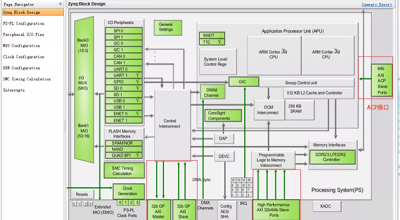

上面介绍了AMBA总线中的两种,下面看下我们的主角—AXI,在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议。其中三种AXI总线分别为:

Xilinx VCU129评估套件设计用于Virtex UltraScale+™ XCVU29P-L2FSGA2577EES9818 FPGA,能够评估和开发56G PAM4应用。该评估套件设有多个常见的高速互连、板载存储器以及PCIe Gen 3接口。

Xilinx Zynq® UltraScale+™ MPSoC 技术助力斯巴鲁基于视觉的高级驾驶辅助系统(ADAS)新一代 EyeSight。集成在全新斯巴鲁 Levorg 车型的新版 EyeSight 系统,将为其提供包括自适应巡航控制、行车道保持辅助和预碰撞制动等先进特性,将一流的安全技术交付至消费者手中。

这篇博客主要记录Vivado中除法IP的注意事项,遇见一些新的知识点应该做相应的笔记。

Rapanda 提供了在 FPGA 上运行的内联端到端流管道。Rapanda 为即将到来的 Event Tsunami 提供大数据流处理和机器学习的加速。