【视频】5G CU 加速

judy 在 周二, 08/25/2020 - 10:42 提交

该视频演示了使用基于 Xilinx FPGA 的网络加速卡在虚拟基站中进行 CU 处理的优势。

该视频演示了使用基于 Xilinx FPGA 的网络加速卡在虚拟基站中进行 CU 处理的优势。

本应用说明介绍了选择串行外设接口(SPI)闪存作为Xilinx 7系列FPGA的配置存储器存储的优势以及实现该解决方案的细节。

Grovf 现在提供其卸载引擎 Hyperon,它是一组在 FPGA 芯片上实现的基本编程算法,与简单易用的主机驱动程序集成。Hyperon 提供算法的加速版本,例如:正则表达式(RegEx,几乎完全支持)、文本相似性匹配、搜索、排序、线性代数(矩阵转置、点积、范数平方、矩阵相乘)以及无损数据压缩等

在此演示视频中,我们将介绍 O-RAN gNB-DU L1 硬件加速和前传卸载。

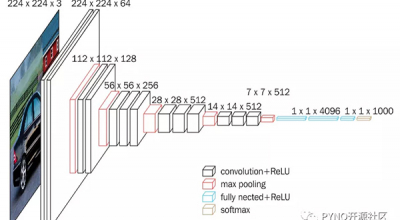

上期推送为大家带来了A班的优秀作品合集。本期,小编为大家带来了B班优秀作品的基于PYNQ的SSD目标检测系统项目。B班的作品相较于A班更有挑战性,内容也更丰富一些。本篇推送主要介绍设计概述,如果有想要亲自尝试本系统的同学,请复制下方Github链接前往GitHub,即可看到本项目的开源代码哦!

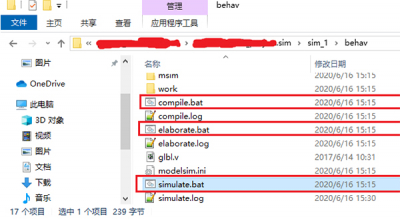

芯片设计从RTL代码一直到最后流片的GDSII文件,都是文本文件,因此,掌握文本分析处理语言是集成电路设计的一项重要的基本功。本文是孙义雯同学采用Python语言实现的Vivado和Modelsim联合仿真的自动化脚本,已经在实际项目中经过较长时间的检验,今天开源出来,供大家学习,欢迎留言交流心得体会和改进建议

PS 和外部接口之间的通信主要是通过复用的输入 / 输出( Multiplexed Input/Output,MIO)实现的,它提供了可以做灵活配置的 54 个引脚,这表明外部设备和引脚之间的映射是可以按需定义的。这样的连接也可以通过扩展 MIO (ExtendedMIO,EMIO)来实现

在数据处理中,对原始数据进行重塑或重新排序并创建多个副本是很常见的行为。无论执行任何新步骤,都会创建新副本。随着程序的增大,占用的内存也会增大,我几乎从未考虑过这个问题,直到遇到了“内存不足”错误。

跟随 Liam Madden,了解如何使用 Xilinx 技术来部署 5G。

想成为一名FPGA工程师,对FPGA的结构是必须要掌握的。FPGA芯片主要是:可编程I/O单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块这六部分组成。