【视频】Xilinx 4x100G FlexE 和 400GbE 连接以太网联盟和 OIF 实现互操作

judy 在 周五, 09/18/2020 - 09:38 提交

观看 Xilinx 技术的现场演示,了解如何使用四个绑定的 100 GbE 接口在 Flex 以太网 (FlexE) 网络上桥接两个 400 千兆位以太网 (400GbE) 网络。

观看 Xilinx 技术的现场演示,了解如何使用四个绑定的 100 GbE 接口在 Flex 以太网 (FlexE) 网络上桥接两个 400 千兆位以太网 (400GbE) 网络。

有工程师反映,在编译PetaLinux工程时,出现大量Taskhash mismatch错误。工程还没有编译完成,检查build.log,已经出现超过200个的Taskhash mismatch错误

凭借 Xilinx® Alveo™ 的联网和计算加速,实现基于无监督机器学习的网络防御。

Vitis统一软件平台可以在包括FPGA、SoC和Versal ACAP在内的异构Xilinx平台上开发嵌入式软件和加速应用程序。它为加速边缘计算、云计算和混合计算应用程序提供了统一的编程模型。

Zynq® UltraScale+™ RFSoC ZCU1275 特性描述套件提供您对集成型 ADC 和 DAC 以及 Zynq UltraScale+ XCZU29DR-2FFVF1760E RFSoC 上提供的 GTY 和 GTR 收发器进行特性描述和评估时所需的一切。

Xilinx 推出 Xilinx T1 电信加速器卡。强大的 5G O-DU 和 vBBU 加速解决方案,专注于为 OEM、运营商和系统集成商提供便利。

有工程师反映,根据MPSoC SWDT在Standalone下的例子xwdtps_polled_example.c,不能实现MPSoC的PS复位。

赛灵思今天宣布面向 5G 网络中的 O-RAN 分布式单元和虚拟基带单元推出 T1 电信加速器卡。T1 卡大幅减少了之前系统所需的 CPU 核数量。与其它竞争方案相比,T1 卡不仅可以降低系统总功耗和成本,同时还支持 O-DU 提供更好的 5G 性能与服务。

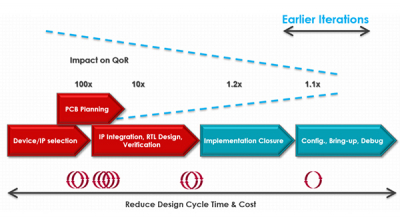

FPGA 设计是有章可循的,如果用的是 Xilinx 的 FPGA,这个“章”就是 UG949。最新版的 UG949 是 2020.1 版本,整个文档共六大章节 306 页(点击此处查看《UltraFast 设计方法指南》)。对于如此之多的内容该如何消化吸收呢?首先,了解一下 UG949 的背景信息。

智能手机似乎迎来了“智能”化的时代,并掀起了物联网(IoT)革命。那么,是什么让 SmartNIC 实现了智能化?是硬件、编程还是其他什么?