ZynqNet解析(八)对IPcore的HLS

judy 在 周四, 03/28/2019 - 10:00 提交

背景:zynqNet运用HLS来实现相应的IPcore。相关HLS过程的信息会打印到console之中。目的:读懂HLS对IPcore代码的HLS过程,具体硬件如何实现。将报告信息存下来用于参考。

背景:zynqNet运用HLS来实现相应的IPcore。相关HLS过程的信息会打印到console之中。目的:读懂HLS对IPcore代码的HLS过程,具体硬件如何实现。将报告信息存下来用于参考。

据外媒报道,人工智能(AI)正在各个行业普及,由于每天都有新的发展成为头条新闻,很难从炒作中挑选出最重要的进展。AI接下来会如何进化?知名市场研究机构CB Insights的分析师调查了各个行业,以确定2019年需要重点关注的25个AI大趋势,从下一代假肢到作物监测等。

边缘计算是5G网络的核心特征,也是结合5G智能物联时代的核心应用特征,针对智能物联场景的特异性,边缘计算对算力需求将呈现定制化个性化的特征,驱动算力产业领域FPGA产业迎来历史性的机会,这也是我们继边缘计算小基站和边缘计算物联应用两篇系列报告之后的最新核心观点。

浪潮宣布已在其NF5280M5、NF5468M5等服务器上完成对赛灵思Alveo U200、Alveo U250 FPGA加速卡的全部认证测试,搭载U200和U250的两款浪潮服务器已可公开购买。NF5280M5、NF5468M5服务器为浪潮的明星产品,分别为AI应用优化、AI云设计,能够针对用户需求进行灵活适配

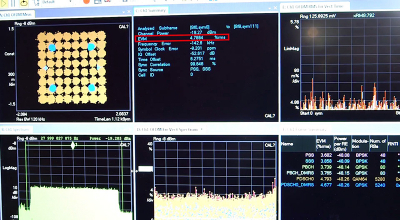

112G PAM4 是业界通向更高带宽的下一步。该演示主要介绍 Xilinx 针对新一代系统提供 112G 的远景。

各方竞争加剧,产品周期缩短,哪些底层技术将最快获益?2019年4月11日,赛灵思 AI 市场发展总监刘竞秀将出席第八届EEVIA年度中国ICT媒体论坛暨2019产业和技术展望研讨会,通过“赛灵思人工智能平台-人工智能边缘计算加速引擎”的主题演讲,分享人工智能时代,灵活应变的赛灵思平台如何与人工智能发展的速度完美匹配,如何从各种传统的计算方案中脱颖而出,成为行业发展的大势所趋

AI 硬件亚洲峰会(AI Hardware Asia Summit) 将要拉开帷幕。这是该系列全球活动的第二个专场,会议主题为 AI 加速器技术以及用于处理深度学习、神经网络和计算机视觉的芯片和系统设计与应用。赛灵思人工智能高级总监单羿将发表题为 “基于FPGA的AI平台、技术、应用和生态系统” 的主题演讲

Xilinx 工具与方法高级应用工程师谢 敏在赛灵思技术日上分享《Alveo 数据中心加速卡快速入门》

时钟信号是FPGA时序逻辑设计中必不可少的条件,一般情况下在FPGA始终资源充裕的情况下通常采用FPGA内部自带的内核生成时钟信号,例如DLL/MMC,但是一旦出现资源不够的情况,就只能另寻他法了

与 O-RAN 联盟成员 AT&T、Anokiwave、Ball Aerospace 和 Keysight 合作,实现了 O-RU 概念验证演示。