聚焦通信与视觉!安富利将携手AMD举办两大系列研讨会!

judy 在 周一, 09/23/2024 - 10:28 提交

本次研讨会,我们将在合肥、重庆、深圳、广州、武汉、青岛、北京等城市展示AMD在视觉应用领域的解决方案

本次研讨会,我们将在合肥、重庆、深圳、广州、武汉、青岛、北京等城市展示AMD在视觉应用领域的解决方案

该层实现用户数据和UDP报文的互转,相比于其它层次的设计,该层的逻辑相对简单。

Verilog语法+:和-:主要用于位选择,可以让代码更简洁。

Artix UltraScale+ XA AU7P是一款拥有超小尺寸、优化成本的车规标准FPGA芯片,针对高级驾驶辅助系统(ADAS)、数字座舱信息娱乐系统(IVI)进行了优化。

本文只讨论整数部分的溢出截位处理,小数部分的处理下篇文章再说。对整数的截位处理,实际上就是对溢出的处理

该层具有接收ARP请求、发送ARP回复,和发送ARP请求、接收ARP回复的功能,并将接收到的对端的地址信息存入cache中

对于企业而言,安全已经成为产品的内置属性,贯穿在整个产品开发周期中。从安全左移到无处不移,业界一直在寻找更加完善的安全解决方案,以满足日益变化的市场需求。

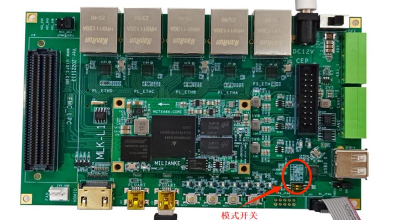

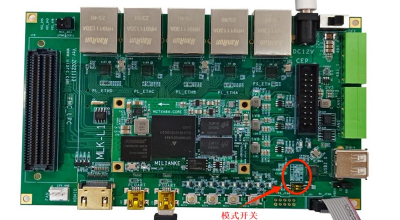

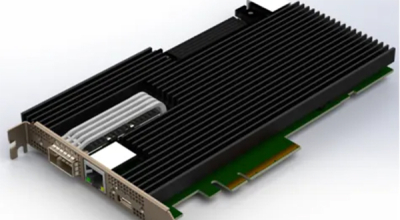

基于FPGA+GPU异构并行计算处理架构设计,内嵌深度学习AI推理框架引擎,可实现图像处理的目标识别加速应用。

AMD 推出了 AMD 汽车车规级( XA )系列的最新成员:Artix™ UltraScale+™ XA AU7P。这款成本优化的 FPGA 符合车规标准

当 CNBC 的Jim Cramer询问AMD首席执行官苏姿丰谈与人工智能巨头Nvidia 的竞争,她表示,炙手可热的半导体行业有足够的空间容纳多家大型企业。