AIE PLIO 简介

judy 在 周五, 01/17/2025 - 17:52 提交

AIE graph通过PLIO与PL(programable logic)连接, 以交换数据, PLIO既可以通过DMA S2MM或者MM2S连接到AI Engine的buffer

AIE graph通过PLIO与PL(programable logic)连接, 以交换数据, PLIO既可以通过DMA S2MM或者MM2S连接到AI Engine的buffer

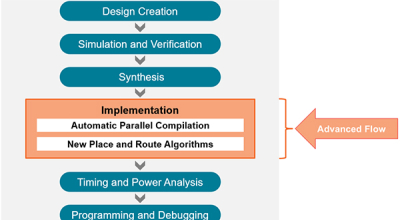

本文介绍了 Versal 的Advanced Flow,这是 Vivado 2024.2 版本提供的一套新的布局布线功能。

本文将详细介绍PolarFire®片上系统(SoC)Discovery工具包的技术细节及其优点。

Example design simulation是同一个器件的GTM仿真。如果需要做两个芯片GTM对接的仿真,可以用两个GTM wizard,生成example

由于Sensor采集到的颜色分量曲线与人眼对颜色分量的感知曲线不一致,所以会导致拍摄的图像呈现在人眼前时感觉与真实世界相去甚远

Versal CPM QDMA EP Design 默认状态下的Setup Debug流程及debug core 时钟,以Vivado 2024.1为例

LCD1602是一种常见的字符液晶显示模块,广泛用于用于AMD 7系列FPGA开发板如Artix AC701、Virtex VC707、Kintex KC705

长期以来,人们对用FPGA实现的创新大张旗鼓,对里面使用的FPGA保持秘而不宣。

用于构建 AMD embeddedsw 组件的旧方法将 .xsa 用作来自硬件人员的交接文件,并将 mdd、mld 和 mss 文件用于不同的软件配置

FPGA可以帮助金融机构提高交易效率、降低风险和优化业务运营,在金融交易领域的典型应用包括