如何使用Microblaze 就地执行(XIP)程序

judy 在 周四, 10/24/2024 - 16:46 提交

本文提供了基于2023.2 Vivado的参考工程,展示如何使用Microblaze 地执行(XIP)程序,并提供一个简单的bootloader。

本文提供了基于2023.2 Vivado的参考工程,展示如何使用Microblaze 地执行(XIP)程序,并提供一个简单的bootloader。

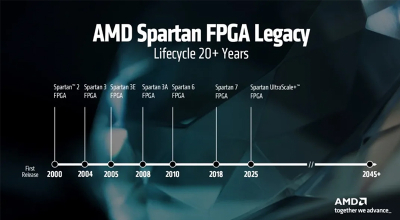

AMD 7 系列器件生命周期延长至 2040 年,AMD UltraScale+™ 器件生命周期延长至 2045 年,AMD Versal™ 自适应 SoC 供应至 2045 年以后

在Vesal器件的DDRMC DDR4/LPDDR4接口上,控制器的系统时钟源通常是由片外的差分时钟所提供的

本指南提供了有关 AMD Vivado™ Design Suite 中包含的 32 位和 64 位 MicroBlaze™ V 软核处理器的信息

本文提供了针对 PCIe 系统中 ATS(地址翻译服务)失效消息问题 (ATS Invalidation message)的排查指南

Altera最新发布的Agilex 3 FPGA系列吸引了行业内广泛关注,这不仅是因为其出色的硬件设计,还在于它针对嵌入式应用提供了高效的AI推理支持和安全保障

Vitis AI Library包含了xdputil工具,可作为板级开发的辅助调试手段,其源代码位于以下位置

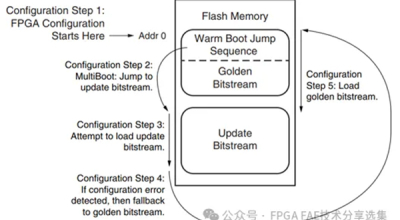

Multiboot是指多镜像启动,比如在FPGA的加载flash里面存放2个或者多个FPGA的配置文件,每个配置文件都可以单独完成FPGA的逻辑配置

AMD Xilinx的Versal器件中的PCIe IP,也可以作为PCIe Host。 AR76647 提供了相关驱动。

我们很高兴地宣布 AMD AMA SDK 1.1.2 版本发布。该版本专注于支持 AMD Alveo™ MA35D 媒体加速卡的其他功能